## IOWA STATE UNIVERSITY Digital Repository

**Retrospective Theses and Dissertations**

Iowa State University Capstones, Theses and Dissertations

2001

## Design techniques and implementations of highspeed analog communication circuits: two analogto-digital converters and a 3.125Gb/s receiver

Ahmed Abdell-Ra'oof Younis Iowa State University

Follow this and additional works at: https://lib.dr.iastate.edu/rtd Part of the <u>Electrical and Electronics Commons</u>

#### **Recommended** Citation

Younis, Ahmed Abdell-Ra'oof, "Design techniques and implementations of high-speed analog communication circuits: two analog-todigital converters and a 3.125Gb/s receiver " (2001). *Retrospective Theses and Dissertations*. 1419. https://lib.dr.iastate.edu/rtd/1419

This Dissertation is brought to you for free and open access by the Iowa State University Capstones, Theses and Dissertations at Iowa State University Digital Repository. It has been accepted for inclusion in Retrospective Theses and Dissertations by an authorized administrator of Iowa State University Digital Repository. For more information, please contact digrep@iastate.edu.

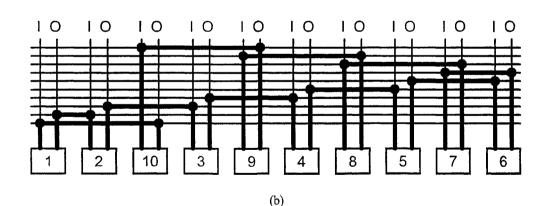

# NOTE TO USERS

This reproduction is the best copy available.

Design Techniques and Implementations of High-speed Analog Communication Circuits: Two Analog-to-Digital Converters and a 3.125Gb/s Receiver

by

Ahmed Abdell-Ra'oof Younis

A dissertation submitted to the graduate faculty

in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

Major: Computer Engineering

Program of Study Committee: Marwan Hassoun, Major Professor William Black Chris Chu Gurpur Prabhu Robert Weber

Iowa State University

Ames, Iowa

2001

Copyright © Ahmed Abdell-Ra'oof Younis, 2001. All rights reserved.

UMI Number: 3098488

UMI Microform 3098488

Copyright 2003 by ProQuest Information and Learning Company. All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

> ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

Graduate College Iowa State University

This is to certify that the doctoral dissertation of

Ahmed Abdell-Ra'oof Younis

has met the dissertation requirements of Iowa State University

Signature was redacted for privacy.

Major Professor

Signature was redacted for privacy.

For the Major Program

## TABLE OF CONTENTS

| Abstract        | viii                                            |

|-----------------|-------------------------------------------------|

| CHAPTER 1.      | Introduction 1                                  |

| CHAPTER 2.      | Terminology And Metrics                         |

| 2.1. Introducti | on                                              |

| 2.2. ADC defin  | nition                                          |

| 2.3. ADC Cha    | racteristics                                    |

| 2.3.1. Resol    | ution and Accuracy                              |

| 2.3.2. Bins :   | and Trip Points                                 |

| 2.3.3. Gain     | and Offset                                      |

| 2.3.4. INL a    | and DNL                                         |

| 2.3.5. SNR,     | SNDR and ENOB                                   |

| 2.3.6. Dyna     | mic Range and SFDR15                            |

| 2.3.7. Laten    | cy15                                            |

| 2.3.8. Apert    | ure Jitter                                      |

| 2.3.9. PSRF     | R (Power Supply Rejection Ratio)                |

| 2.3.10. THI     |                                                 |

| 2.4. Conclusio  | ns                                              |

| References      |                                                 |

| CHAPTER 3.      | ADC Architectures                               |

| 3.1. Introducti | on                                              |

| 3.2. Flash AD   | Cs                                              |

| 3.2.1. Adva     | ntages                                          |

| 3.2.2. Limit    | ations                                          |

| 3.3. Two-step   | Flash ADCs21                                    |

| 3.4. Folding A  | DCs                                             |

| 3.5. Multistep  | ADCs                                            |

| 3.6. Successiv  | e Approximation and Algorithmic converters ADCs |

| 3.6.1. Succe    | essive Approximation ADCs                       |

| 3.6.2. Algor    | rithmic Converters ADCs                         |

| 3.7. Pipeline A | ADCs                                            |

| 3.8. Parallel P | ipeline ADCs                                    |

| 3.9. Oversampling ADCs                                        |    |

|---------------------------------------------------------------|----|

| 3.9.1. Sigma Delta Modulation                                 |    |

| 3.10. Conclusions                                             |    |

| References                                                    |    |

| CHAPTER 4. Pipeline ADCs                                      |    |

| 4.1. Introduction                                             |    |

| 4.2. Pipeline Building Blocks                                 |    |

| 4.2.1. Operational Amplifier                                  |    |

| 4.2.2. Common Mode feedback circuit                           |    |

| 4.2.3. CMOS Comparator design                                 |    |

| 4.3. Error Sources in Pipeline ADCs                           |    |

| 4.3.1. Capacitor Mismatch                                     |    |

| 4.3.2. Comparator Offsets                                     | 51 |

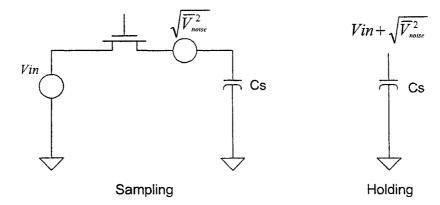

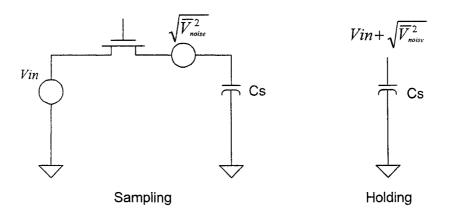

| 4.3.3. Thermal noise                                          | 53 |

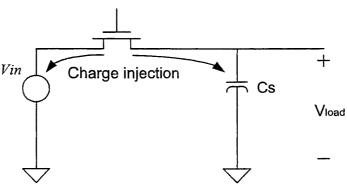

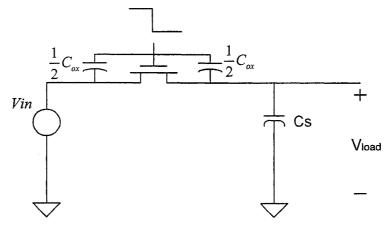

| 4.3.4. Charge injection and Clock feedthrough                 | 54 |

| 4.4. Channel-related errors                                   | 56 |

| 4.4.1. Channel Gain mismatches                                | 56 |

| 4.4.2. Channel offset mismatches                              | 58 |

| 4.4.3. Timing mismatch and Jitter                             | 59 |

| 4.5. Conclusions                                              | 61 |

| References                                                    | 62 |

| CHAPTER 5. Implementation Of 10-Bit And 100 Ms/S Pipeline ADC | 63 |

| 5.1. Introduction                                             | 63 |

| 5.2. 10-bit Pipeline ADC                                      | 63 |

| 5.2.1. Operation of one stage of the ADC                      | 65 |

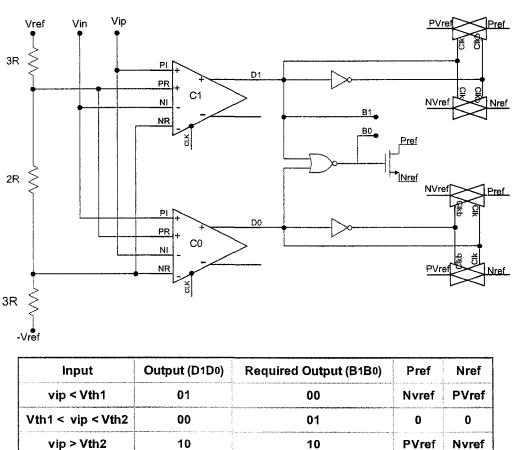

| 5.2.2. Operation of the subADC                                | 68 |

| 5.2.3. Operation of the comparators                           | 69 |

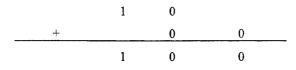

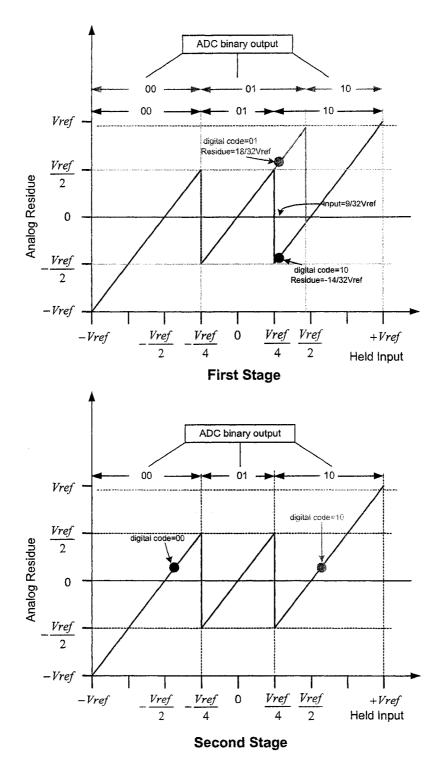

| 5.2.4. Digital error correction                               | 71 |

| 5.2.5. Implementation of one stage                            | 74 |

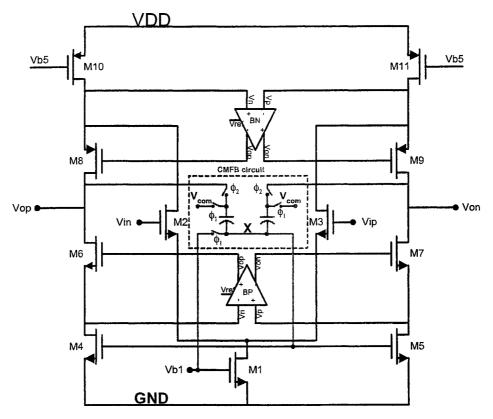

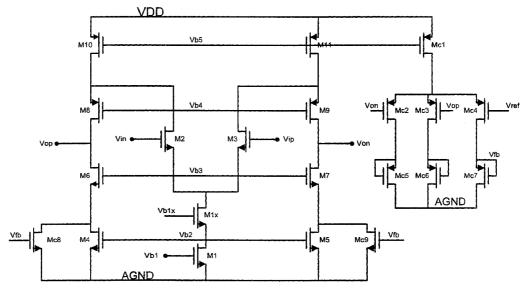

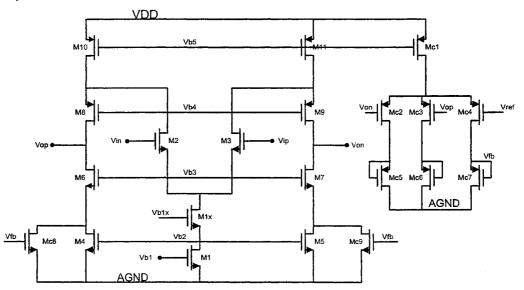

| 5.2.6. Design of the operational amplifier                    | 76 |

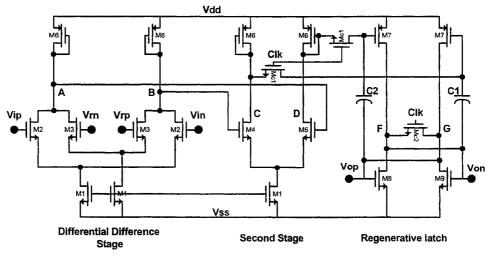

| 5.2.7. Comparator implementation                              | 82 |

| 5.2.8. Capacitor design in TSMC 0.25u Process                 | 84 |

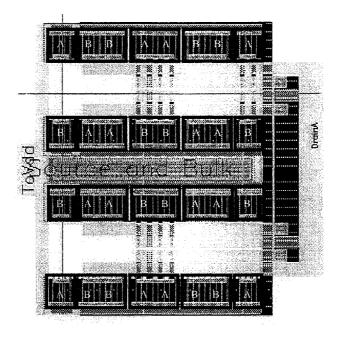

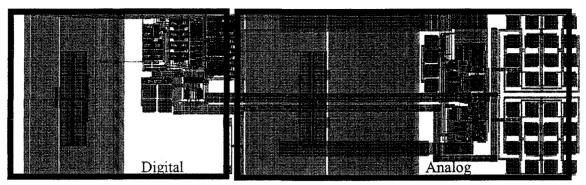

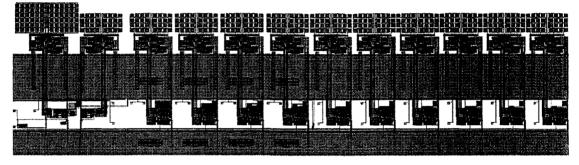

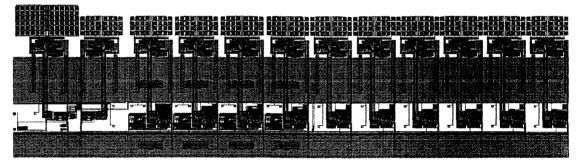

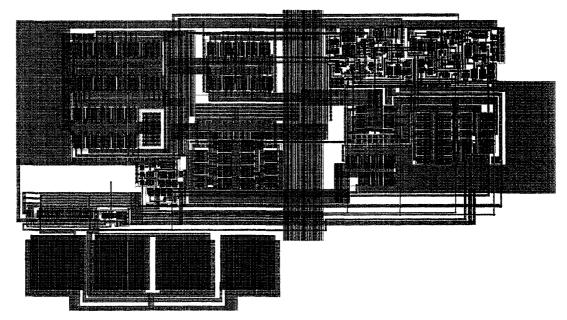

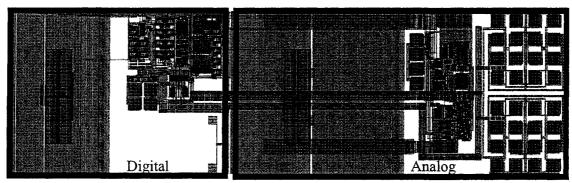

| 5.3. Layout                                                   | 85 |

| 5.3.1. Operational amplifier layout                           | 85 |

| 5.3.2. Stage layout                                           | 85 |

|                                                               |    |

| 5.3.3. Overall Layout                                    |  |

|----------------------------------------------------------|--|

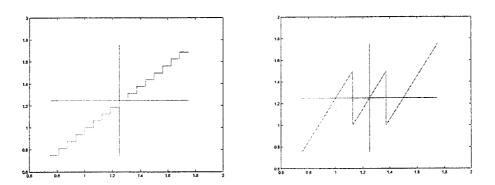

| 5.4. Testing Results                                     |  |

| 5.5. Conclusions                                         |  |

| References                                               |  |

| CHAPTER 6. ADC Error Correction And Calibration          |  |

| 6.1. Introduction                                        |  |

| 6.2. Analog versus digital calibration                   |  |

| 6.2.1. Over-range and under-range stages                 |  |

| 6.2.2. 1.5-bit per stage                                 |  |

| 6.2.3. Stage gain < 2                                    |  |

| 6.2.4. Pros and cons for the above designs               |  |

| 6.3. Capacitor Error-Averaging                           |  |

| 6.4. Continuous calibration                              |  |

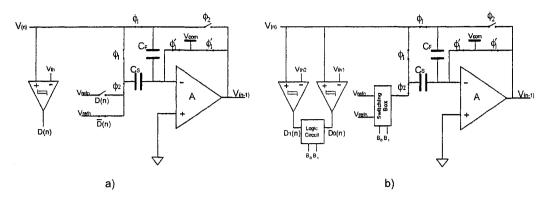

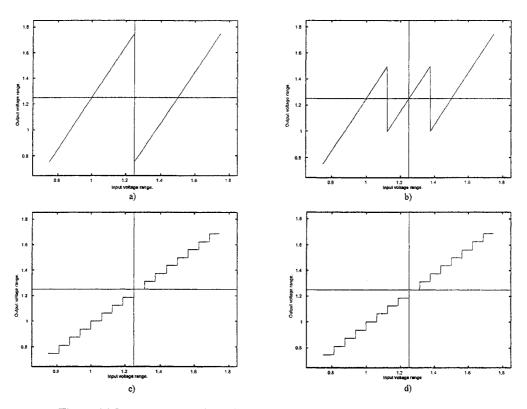

| 6.5. Proposed Single Path calibration algorithm          |  |

| 6.5.1. Overview                                          |  |

| 6.5.2. Comparator offsets                                |  |

| 6.5.3. Correction Algorithm                              |  |

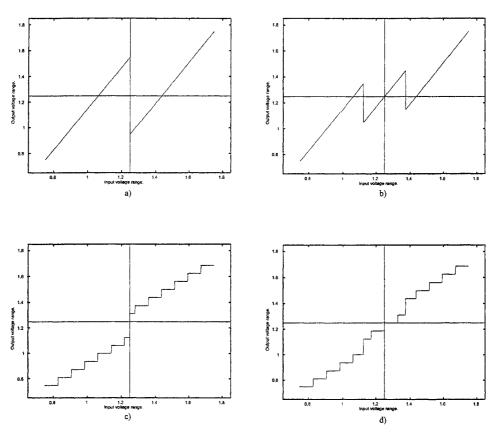

| 6.5.4. Gain and DAC measurement algorithm                |  |

| 6.6. Multipath Calibration                               |  |

| 6.6.1. Gain error randomization                          |  |

| 6.6.2. Channel normalization                             |  |

| 6.6.3. Hardware sharing                                  |  |

| 6.6.4. Digital Calibration                               |  |

| References                                               |  |

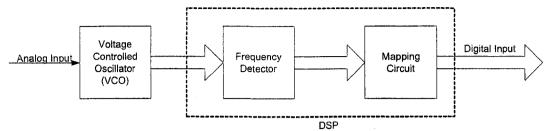

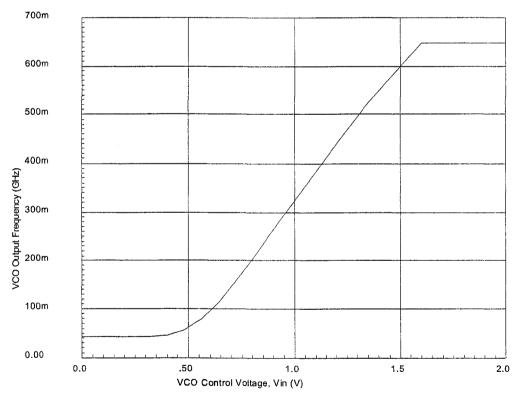

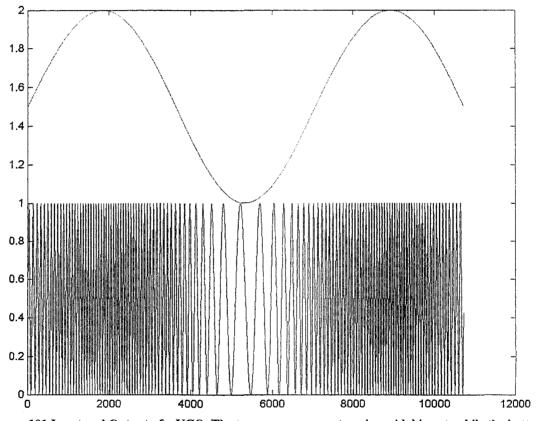

| CHAPTER 7. VCO-Based ADCs                                |  |

| 7.1. Introduction                                        |  |

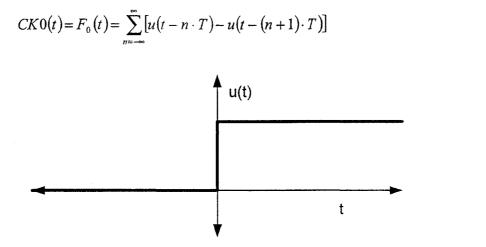

| 7.2. Architecture                                        |  |

| 7.3. Frequency Detector Circuit                          |  |

| 7.3.1. Introduction and overview                         |  |

| 7.3.2. Proposed solution                                 |  |

| 7.3.3. Implementation                                    |  |

| 7.3.4. Derivation of Maximum Error in the FD Measurement |  |

| 7.3.5. Example                                           |  |

| 7.4. The mapping Circuit                                 |  |

| 7.5. ADC Overall Picture                                 |  |

| 7.6. Summary      |                                                                     | 149          |

|-------------------|---------------------------------------------------------------------|--------------|

| References        |                                                                     | 151          |

| CHAPTER 8. H      | ligh Speed Receiver Design                                          | 152          |

| 8.1. Introduction |                                                                     | 152          |

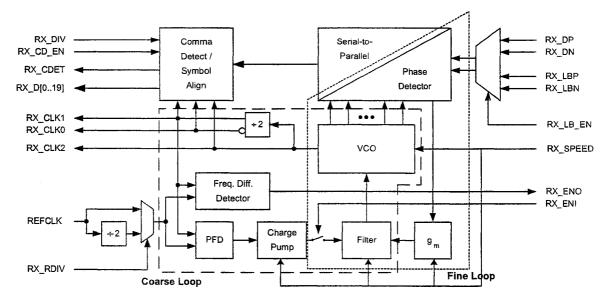

| 8.2. Architecture |                                                                     | 153          |

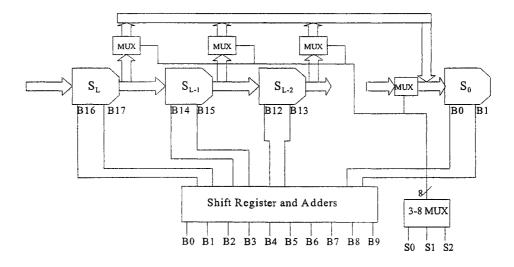

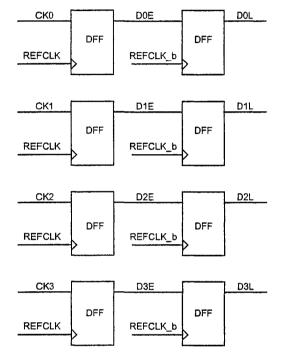

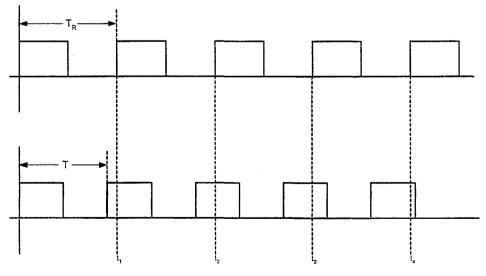

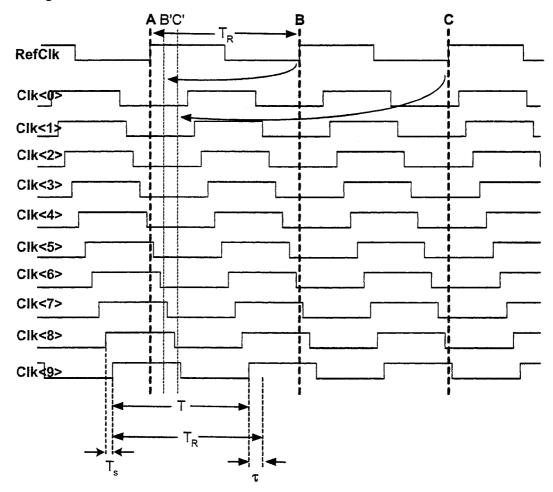

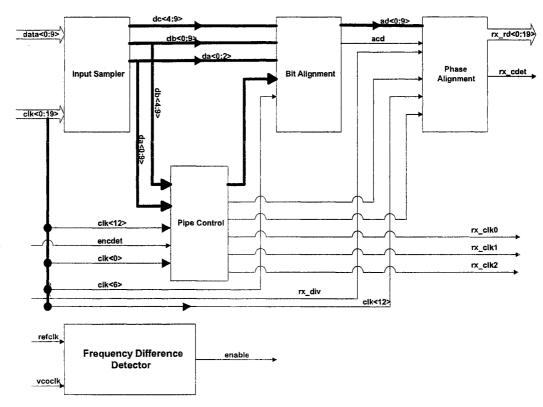

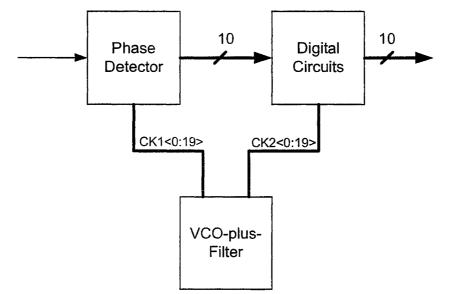

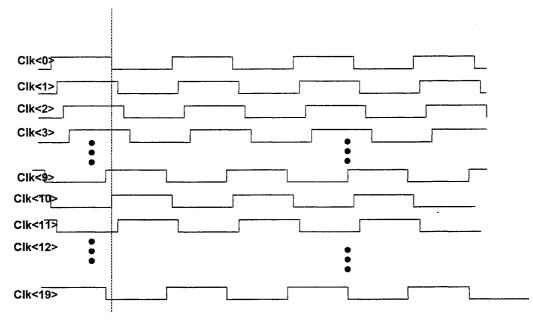

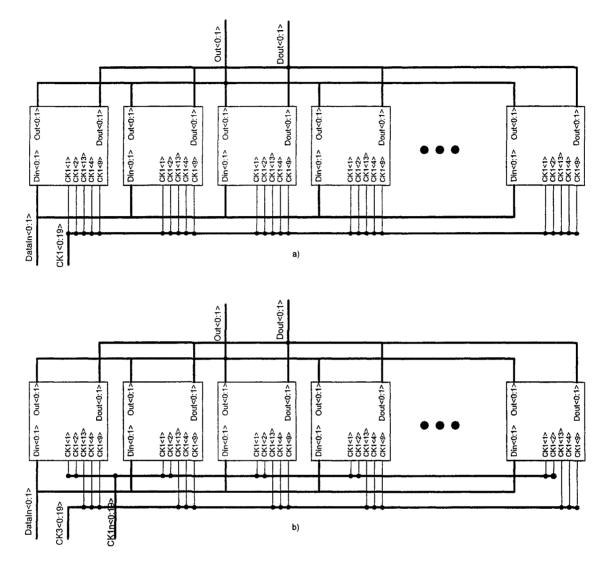

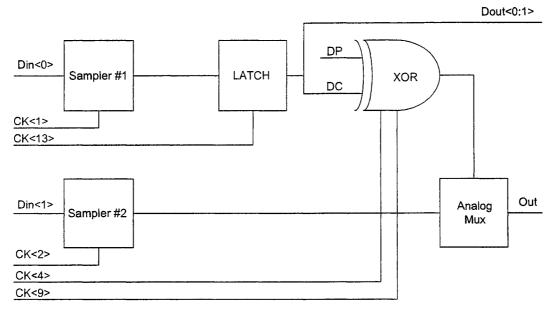

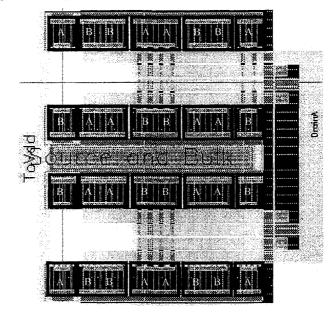

| 8.2.1. The De     | serializer                                                          | 154          |

| 8.2.2. The Co     | arse Loop                                                           | 155          |

| 8.2.3. The Fin    | e Loop                                                              | 156          |

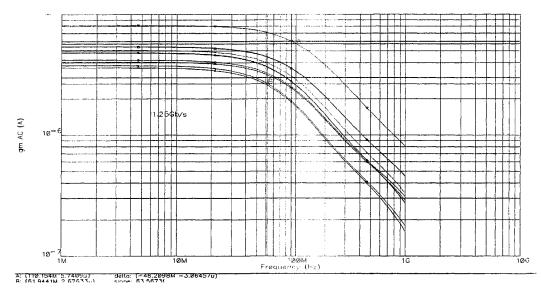

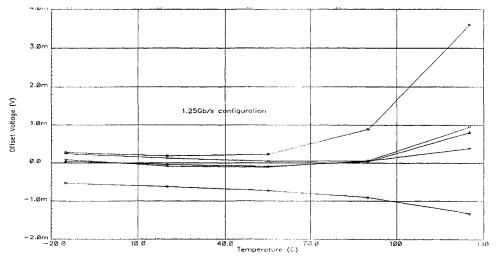

| 8.2.4. The Gn     | 1 Circuit                                                           | 158          |

| 8.3. Performance  | e Enhancement                                                       | 161          |

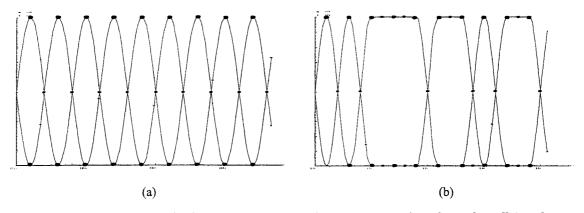

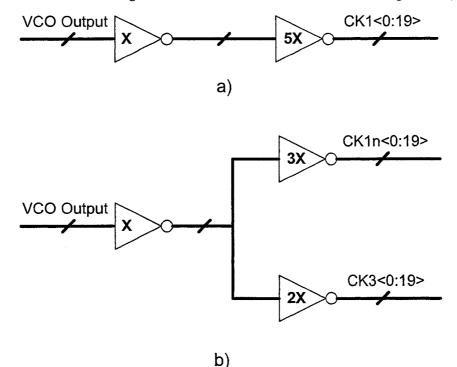

| 8.3.1. VCO Ji     | tter Minimization                                                   | 161          |

| 8.3.2. Buffer \$  | Separation                                                          | 162          |

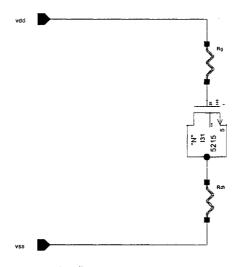

| 8.3.3. Power S    | Supply Noise Reduction                                              | 163          |

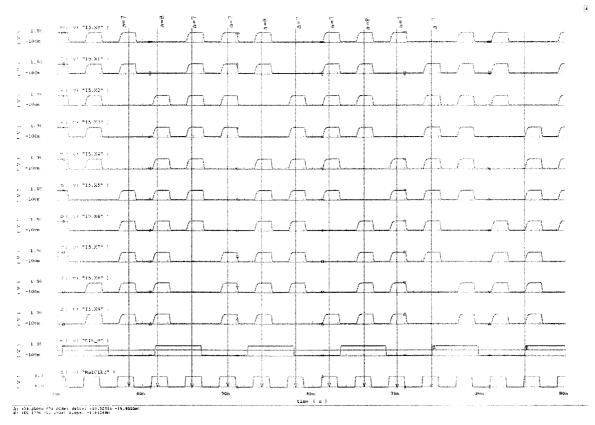

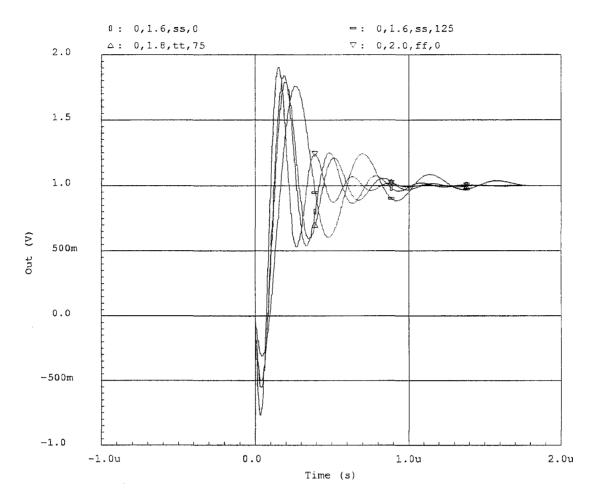

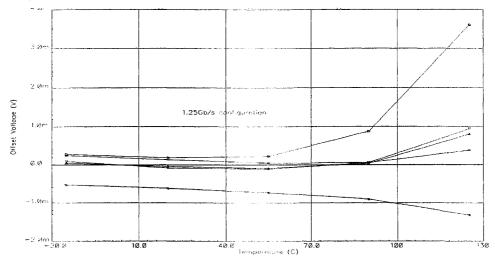

| 8.4. Top Level F  | Receiver Analog Simulations                                         | 165          |

| 8.5. Receiver De  | evelopment                                                          | 167          |

| 8.5.1. VCO la     | yout                                                                | 169          |

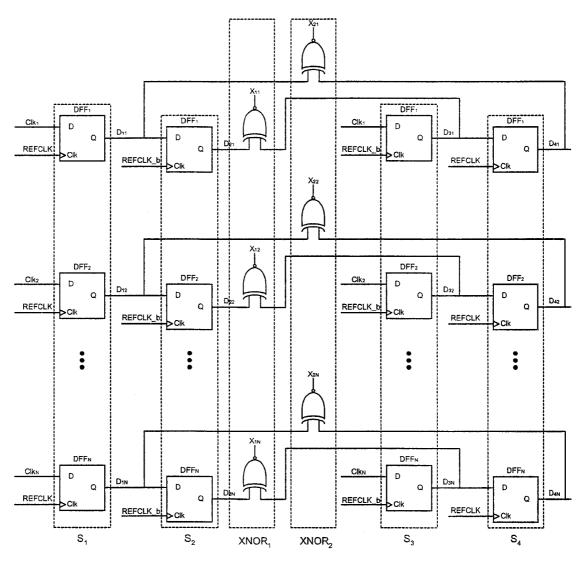

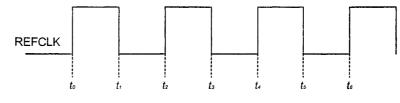

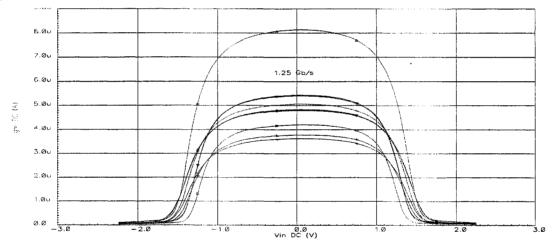

| 8.5.2. Parasiti   | c insensitive clocking scheme                                       | 172          |

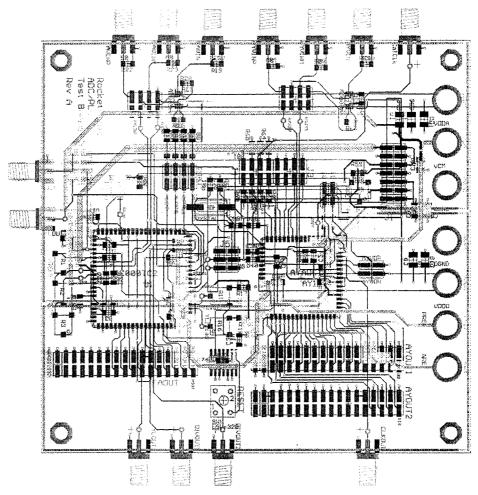

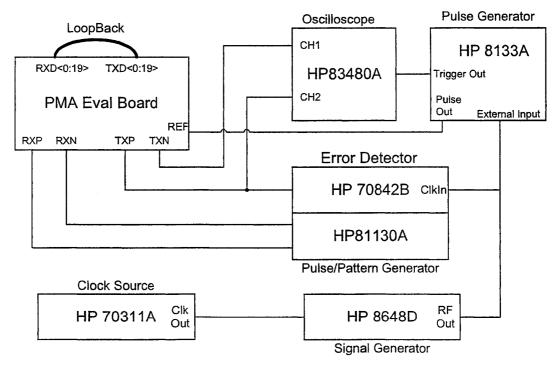

| 8.6. Test Setup.  |                                                                     | 1 <b>7</b> 6 |

| 8.7. Measured R   | esults                                                              | 177          |

| 8.7.1. Jitter Te  | blerance                                                            | 177          |

| 8.8. Summary A    | nd Conclusions                                                      | 179          |

| References        |                                                                     | 180          |

| CHAPTER 9. I      | Design Techniques and Engineering Practice For High-Speed Analog IC | Cs 181       |

| 9.1. Introduction | 1                                                                   | 181          |

| 9.2. Design of th | e operational amplifier                                             |              |

| 9.2.1. Operati    | onal Amplifier: Theoretical Analysis                                | 182          |

| 9.2.2. Operati    | onal Amplifier: Practical Design                                    |              |

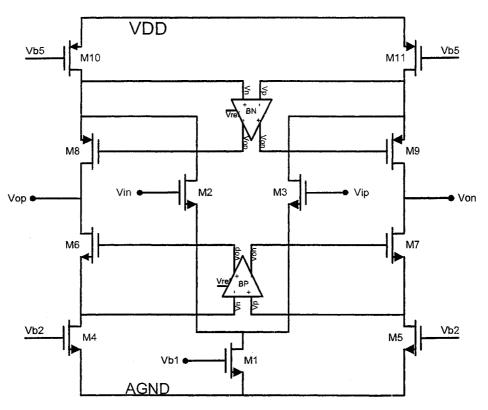

| 9.2.3. CMFB       | circuit design of the main amplifier                                | 187          |

| 9.2.4. CMFB       | circuit design of the boosting amplifiers                           | 187          |

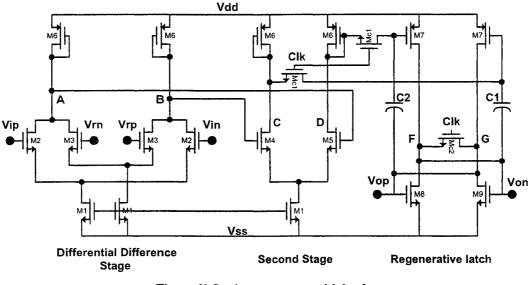

| 9.3. Comparator   | implementation                                                      |              |

| 9.4. Metal dapad  | tor design                                                          | 190          |

| 9.5. Thermal no   | ise                                                                 | 192          |

| 9.6. Charge inje  | ction                                                               | 193          |

| 9.7. Clock feedt  | hrough                                                              | 195          |

| 9.8. Gm cells     |                                                                     | 195          |

| CHAPTER 10. Conclusions                                      |  |

|--------------------------------------------------------------|--|

| References                                                   |  |

| 9.11. Conclusions                                            |  |

|                                                              |  |

| 9.10.3. Overall Layout.                                      |  |

| 9.10.2. ADC Stage layout                                     |  |

| 9.10.1. Operational amplifier layout                         |  |

| 9.10. Layout                                                 |  |

| 9.9. Parasitic insensitive clocking Scheme                   |  |

| 9.8.1. Designing for Figures of Merit and Simulation Results |  |

## Abstract

Low-cost and high performance analog building blocks are essentials to the realization of today's highspeed networking and communications systems. Two such building blocks are analog-to-digital converters (ADCs) and multi-gigabit per second transceivers. The ADCs are paramount to translating the real world analog signals into the digital processing world. The multi-gigabit transceivers are becoming a necessity for high-speed systems and chips to transfer the enormous amount of digital data between each other. This thesis addresses two different ADC architectures and a 3.125Gb/s receiver architecture.

The first ADC architecture is a 10-bit, 100MS/s pipeline ADC. Techniques that enhance the gainbandwidth of the operational amplifier, a key building block in analog-to-digital converters, as well as to increase its dc gain are presented. Layout techniques to reduce the effect of parasitics on the performance of the ADC are also discussed. Since any ADC will have inherent errors in it, two calibration techniques that reduce the effect of these errors on the performance of the ADC are also presented.

In this thesis, the design of the ADC as well as the implementation of those techniques will be presented and discussed.

For the second ADC, a new architecture is proposed that is capable of achieving higher performance than many current ADC architectures. The new architecture is based on a voltage controlled oscillator and a frequency detector. One reason for the high performance of the new ADC is the novel design of the frequency detector. This thesis includes detailed analysis as well as examples to illustrate the operation of the frequency detector.

Designing high-speed CMOS transceivers is a challenging process, especially, when using digital CMOS process that exhibits poor analog performance. Circuit implementation and design techniques that are used to design and enhance the performance of the receiver block of a 3.125Gb/s transceiver in a 0.18u digital CMOS process will be presented and fully explained in this thesis. Silicon results have shown that these techniques have resulted in outstanding and very robust receiver performance under different operating conditions.

The thesis also includes a chapter on design techniques and engineering practices for high speed analog ICs. These techniques were used extensively in the design of the ADC as well as the receiver.

### **CHAPTER 1.** Introduction

With the great advances in digital circuits, the demand on analog circuits increases as well. There are digital systems that require analog front-end (AFE) subsystem to make them alive. One example is communication systems. This is mainly due to the nature of the signals being transmitted. Signals are analog by nature.

Even if a signal is transmitted as a digital one over a cable or in the air, after a while, it will no longer be digital. Noise, interference, attenuation and many other impairments will distort the signal and make it look like an analog one.

Although analog circuits can understand digital signals, digital circuits cannot understand analog signals. This requires analog signals to be handled by analog circuits.

In this thesis, analog design techniques and implementations of high-speed circuits that are used to work on analog signals are presented.

It is important to familiarize the reader of this thesis with some terminology that will be used throughout the thesis. CHAPTER 2 presents the terminology and metrics that are used in data converters, as they are one of the most important and challenging analog circuits in many systems.

Analog-to-digital converters (ADCs) are used in digital systems whenever the input is an analog signal. The ADC converts the analog signal into an equivalent digital value that can be used by the digital system. CHAPTER 3 presents some ADC architectures that are commonly used to do the job. In particular, CHAPTER 4, talks about the pipeline ADC architecture in more details as it is being chosen to design an ADC that is capable of achieving 10 bits of resolution when running at 100MHz. The details of the implementation of this ADC are presented in CHAPTER 5. CHAPTER 6 presents the techniques that are commonly used to enhance the performance of data converter circuits. In addition, it presents two new algorithms that can be used to enhance what is called the *DNL* of an ADC. In CHAPTER 7, a new architecture of ADCs is presented. This architecture is not only based on a new concept, but it also has the potential for achieving higher performance with lower power and smaller silicon area than current architectures.

When it comes to the design of any system, time-to-market plays a great role in deciding on a specific architecture. The new architecture uses a very common analog block called *voltage-controlled oscillator (VCO)* as its main conversion engine. VCOs are used mainly in communication systems as well as in clock synthesizers. This block is well researched and many of its design issues are well known to the analog

designers. This, in turn, will have a great impact on the time-to-market factor. The new architecture also includes a novel *frequency detector* (FD) circuit that enables the ADC to run at very fast speeds.

CHAPTER 8, presents analog design techniques as well as circuit implementation of a CMOS 3.125Gb/s receiver. This receiver achieved high performance with minimum power consumption as will be shown in the measurement section of the same chapter.

All the design techniques and engineering practices used in this dissertation are collected in CHAPTER 9. These techniques can be applied in any analog system.

The conclusions of this dissertation are presented in CHAPTER 10, which provides a brief summary of each chapter of this dissertation as well as the contributions of this research.

## **CHAPTER 2.** Terminology And Metrics

#### 2.1. Introduction

This chapter contains the necessary material that is required to understand data converters, their function and how to differentiate between them. The first section in this chapter will define the analog-to-digital converter as a system and identify its function. There are many data converter architectures in the market and each one has its own advantages over the others. In order to characterize them and quantify their performance, many parameters have to be evaluated. Some of the most common parameters and their definitions will be covered in the section 2.3.

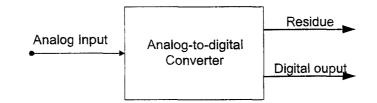

Figure 1 Analog-to-Digital Converter system.

#### 2.2. ADC definition

An Analog-to-Digital Converter (ADC) is a device that has an analog input and produces a digital output that is equivalent to the analog input. The analog input is an electrical signal that might be a current or a voltage. An ADC can be modeled as shown in Figure 1, which shows that in addition to the digital output, another analog output, called the *residue*, might also be generated by the ADC, although in almost all practical ADCs this output is ignored. The ADC performs what is called *quantization* on the input signal. Quantization is the process of transforming a continuous analog signal by a set of digital values that closely approximates the original signal. A good way of illustrating the quantization process is by an example.

#### Example 1.

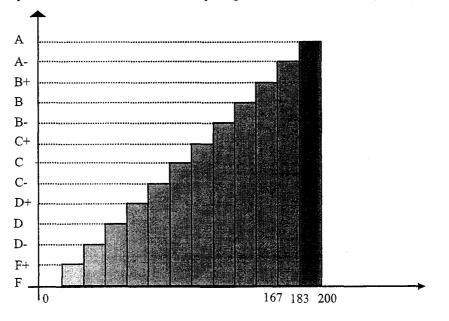

Consider the grading system at school, where the instructor has to submit the grades using the system A, A-, B+, B, B-, ..., F. The instructor gathers the grades during the semester out of 200, and at the end of the semester, he/she *quantizes* those grades to the equivalent letter system. For instance, a

student whose total is 172 will be given a B+, while another student whose total is 165 will be given a B.

Figure 2 depicts this process. If another student has a total of 180, he will get a  $\mathbf{B}$ +, too. The  $\mathbf{B}$ + grade can be assigned to any total in the range of 167 to 183. According to Figure 2, the quantization level of  $\mathbf{B}$ + is 167, so, any total that lies in the range 167–183 will be assigned a  $\mathbf{B}$ +. The difference between any total and its quantization level is equivalent to the residue, while the grades; A, A-, B+, ..., F are equivalent to the digital output in the ADC.

The digital output will not exactly reflect the input signal, rather, it will be equivalent to the closest quantization level smaller than the input signal. Consider the following example:

Figure 2 The grading system as a quantization process.

#### Example 2.

Suppose that we have an ADC that quantizes an input signal into integer values. The input signal is a continuous time voltage signal that ranges from 0 to 5V. If the input signal value is, say, 4.3V, the digital output will be 4 and the residue will be (4.3V - 4.0V) = 0.3V. Note that when the residue was calculated, the exact analog equivalent value was subtracted from the input signal value.

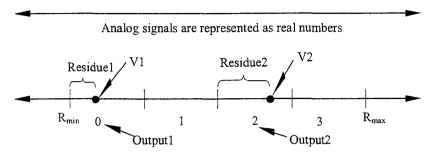

If we represent the analog signals by the real numbers line, an ADC can be viewed as dividing the real line into subranges and the input signal is mapped to one of those subranges. Those subranges are given codes and the ADC generates the code of the subrange to which the input signal belongs, in addition to the location of the input signal in that subrange. This is illustrated in Figure 3.

Figure 3 ADC system as a real line.

Figure 3 illustrates the function of the ADC. The input signals are represented as dots on the real line. Given the first value, V1, is an input to the ADC, the ADC will generate a digital output, 0, which says that the input value occurred in the subrange that is marked by the code 0. For the second value, V2, the ADC will generate a digital value, 2, that correspond to the subrange to which V2 belongs. Note that the residue values are different for the two input values.

#### 2.3. ADC Characteristics

ADCs are categorized according to their ability to digitize the input signal range into distinct subranges or levels. The more number of levels the ADC is able to generate, the closer the equivalent value of the digital code generated by the ADC is to the actual input signal, which, in turn, means the smaller the residue is. Each level is assigned a unique code or number. Although it is not necessary, those numbers are always represented in binary form. For example, if we have 4 levels in the input signal range, the first level can be given the code 00, the second one can be given 01, the third 10 and the last one can be given the code 11. The assignment of those codes to the levels, called *code assignment*, can also be useful as will be shown later since, if they are chosen carefully, they might relax the design of some parts of the ADC. An easier and more practical way to categorize an ADC can be achieved by taking  $log_2(number of levels)$ , which is generally referred to as *the number of bits*. In practice, we might encounter a 13-bit ADC, which means that the ADC is able to digitize the input signal into one level out of  $(2^{13} = 8192)$  levels that span over the input signal range.

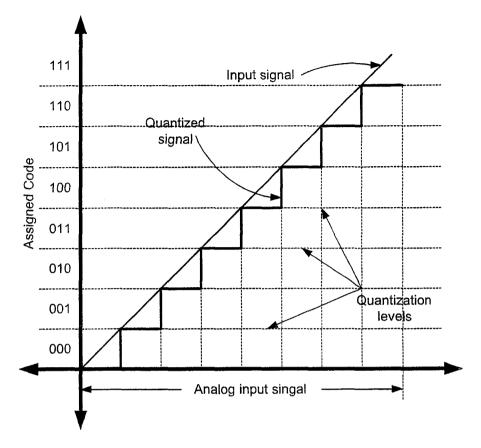

Since the ADC is a system, it must have a transfer function that relates the digital output to the analog input and this is shown as the solid line in Figure 4 for an ideal one. An ideal ADC is one whose behavior agrees completely with theoretical calculations of its parameters, i.e., it has ideal parameters. Those parameters will be illustrated as we proceed through the following sections.

Figure 4 ADC transfer characteristic

#### 2.3.1. Resolution and Accuracy

Resolution is the number of bits an ADC can have, and it is a measure of the ability of the ADC to digitize the input signal's range into larger number of subranges. So, an 8-bit ADC means that the resolution of the ADC is 8 bits or equivalently, the ADC can resolve 8 bits, and it can digitize the input signal's range into  $2^8$  subranges. If the overall range of the ADC is normalized to 1, i.e., the range becomes from 0.0 to 1.0, then the size of a subrange is called the *Least Significant Bit*, LSB. Mathematically,

$$LSB = \frac{overall\ signal\ range}{2^n} \tag{1}$$

where *n* is the number of bits the ADC can resolve. For example, a 1 LSB of a voltage signal that ranges between 0 and 5V in a 6-bit ADC is  $5.0/2^6 = 78.125$  mV.

The accuracy of an ADC is defined as the precision with which the subrange is calculated. The accuracy of the ADC is usually related to the *DNL* of the ADC as will be described later. As an example to the accuracy, consider an 8-bit ADC with accuracy of 9 bits. This means that each subrange width is at most

### 2.3.2. Bins and Trip Points

As the ADC divides the range of the input signal into subranges, those subranges are called *bins*, (Bs). The value of the input signal at which the ADC changes the quantization from one bin to a next one is called a *trip point*, (TP). Those two definitions will be used frequently when we talk about the error sources in an ADC system later on. Bins and TPs will be illustrated in the following example.

#### Example 4.

Consider an ideal 3-bit ADC with a voltage input signal that ranges from 0V to 5V. If the ADC is ideal, it will have ideal bins and ideal TPs. The ideal bin size will be:

$$\frac{(5-0)}{2^3}V = \frac{5}{8}V = 0.625V$$

(2)

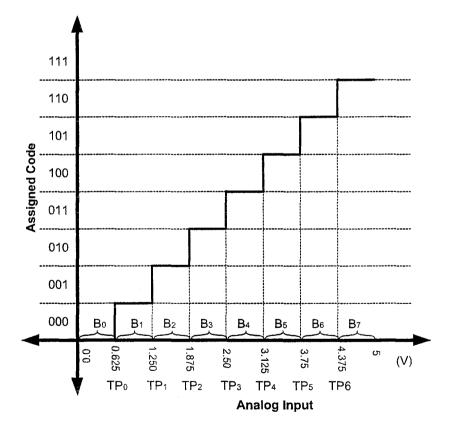

The ADC bins and TPs are shown in Figure 5.

Figure 5 Bins and Trip Points.

Figure 5 shows the bins to which the ADC divides the input signal range. As an example, the first bin,  $B_0$ , covers the range from 0V to 0.625V, while,  $B_3$ , covers the range 1.875V to 2.5V. Table 1 shows the values of the trip points of the ADC. If the input signal value is less than the first trip point, the ADC will quantize that signal into 0V, which means that the ADC will generate a digital value that corresponds to a 0V input signal. If the input signal has a value in  $B_5$ , i.e., between  $TP_4$  and  $TP_5$ , the ADC will quantize it to  $TP_4$ . As will be shown later, this might not be true in general, but it holds for the above example.

| TP0   | TP1  | TP2   | TP3 | TP4   | TP5  | TP6   |

|-------|------|-------|-----|-------|------|-------|

| 0.625 | 1.25 | 1.875 | 2.5 | 3.125 | 3.75 | 4.375 |

Table 1 Trip point values for the 3-bit ideal ADC.

#### 2.3.3. Gain and Offset

In example3 above, an ideal ADC is assumed to quantize the signal exactly as described above, however, in practice, ADCs are not ideal. When an ADC processes the input signal, some kinds of impairments are introduced to the signal. Examples of those impairments are system noise, distortion, and change in ADC parameters due to environmental changes such as drifts in temperature, power supply and process variation. Those impairments will affect the transfer characteristic of the ADC and result in what is called ADC *Errors*. There are two kinds of ADC errors; *linearity* and *nonlinearity* errors.

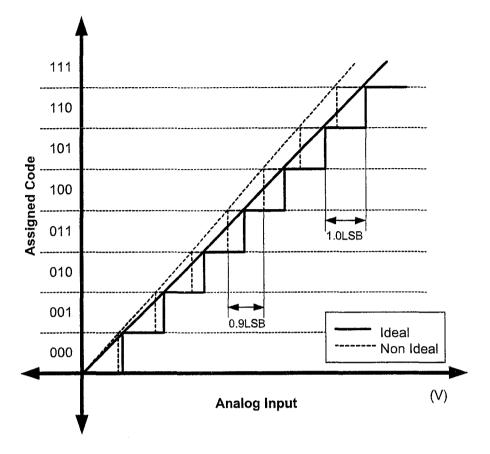

Figure 6 Effect of errors in bin size.

Linearity errors are those kinds of errors that affect all bins of the transfer characteristics by the same amount. One example of this effect might be the reduction of *all* bin sizes by the same value. Ideally, all bin sizes have to be 1 *LSB* wide, but, they all might have a size of 0.9*LSB*. Figure 6 shows two transfer characteristics;

Ideal, which is plotted as a solid line. The edges of the steps are connected by a solid straight line to distinguish them from the second plot.

Nonideal, which is plotted as a dotted line. The edges of the steps are connected by a dotted straight line to distinguish them from the first plot.

The slope of the straight line is called the *gain* of the ADC. The change in the sizes of all bins just described will result in a change in the ADC overall gain, as shown in Figure 6.

Although the straight lines plotted in Figure 6 connect the edges of the steps, in practice, however, there are many ways to plot the straight line, some of those will be discussed in the next subsection.

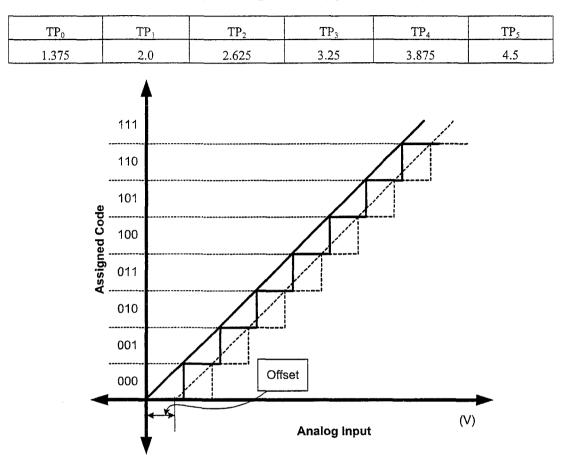

Another example of linearity errors is the drift of *all* trip point values by the same amount. Adrift of 750mV will result in the following TPs shown in Table 2 instead of those in Table 1.

9

Table 2 A linearity error might cause trip points to drift by 0.75V.

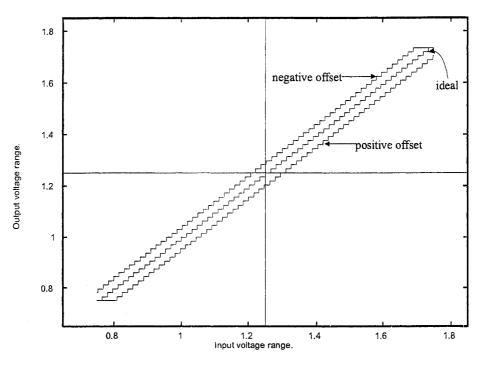

Figure 7 Effect of errors in the trip points.

The effect of this error is that a shift in the transfer characteristic occurs, and it is shown in Figure 7. The shift in the transfer characteristic from the origin point of the coordinate is called ADC *offset*.

Not all the ADCs are built with zero offset. For example, if the noise in the system has a zero average value, then it might be better to introduce an offset in the system so that the ADC will not keep jumping from the first bin to the second when there is no input signal [1]. Hence, the error in ADC offset is the difference between the actual offset and the offset set by design.

In summary, ADC gain is the overall gain of the ADC and it is the slope of the straight line that connects the steps of the transfer characteristic of the ADC. Gain error, on the other hand, is the difference in the gain of the nonideal ADC and the ideal one.

ADC offset is the offset of the straight line from the zero value of the analog input signal. Offset error, on the other hand, is the difference between the nonideal offset and the ideal one.

Nonlinearity errors will be discussed in the following subsection.

#### 2.3.4. INL and DNL.

In most ADC's, the gain and offset specifications are not the most critical ones that determine an ADC's usefulness in specific applications. *Differential NonLinearity* (DNL) and *Integral NonLinearity* (INL) [2], which are considered as nonlinearity errors, are considered the most important specifications for the bulk of ADC applications, because they represent irreducible errors inherent to a practical ADC.

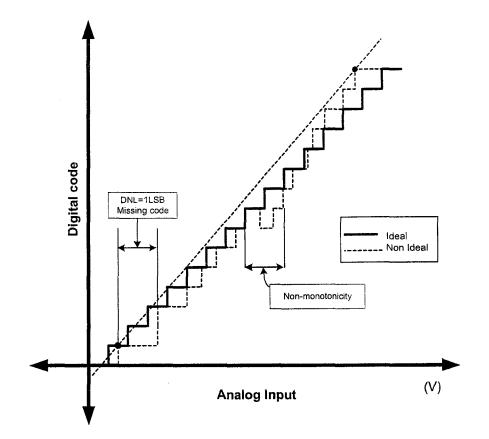

Figure 8 Ideal and nonideal transfer characteristic of an ADC.

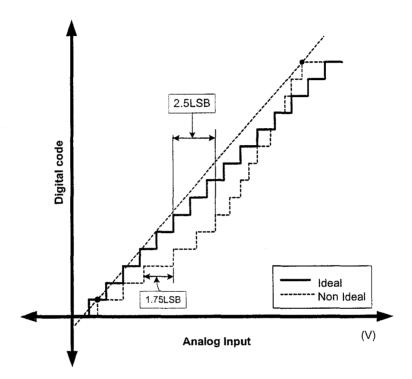

Nonlinearity errors, in general, are those that affect the bins of the transfer characteristic unequally. Figure 8 shows a more practical transfer characteristic of an ADC.

*INL* is defined as the deviation of the transfer characteristic of a practical ADC from the ideal straight line. It is always measured at the quantization levels and expressed in terms of LSBs. There are many ways to draw the straight line that is shown in the figures above, some of those are:

- 1. End Points. A straight line is drawn between the first step edge and the last step edge. Figure 8 shows and INL of 2.5 LSB at  $B_6$ , which happens to be the maximum INL of this ADC. When INL is specified in terms of the deviation from a straight line using this method it is called *end-point* INL.

- 2. Best-straight-line. The straight line is calculated such that the worst-case INL error, i.e., the maximum value of an INL error, is minimized. Usually, the straight line is calculated using least

square fitting curve procedure. INL specified in terms of the deviation from a straight line using this method is called *best-straight-line* INL.

Figure 9 Missing codes and non-monotonicity due to large DNL errors.

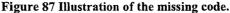

DNL is the difference between the nonideal bin size and the ideal one, which is 1 LSB. As an example,  $B_3$  of the ADC shown in Figure 8 has a DNL of 0.75 LSB. A DNL of 1 LSB results in what is called *missing* code, where one of the quantization levels will be missing in the transfer characteristic. If an ADC has a DNL greater than 1 LSB, then it will result in what is called *non-monotonicity*, where the quantization level of a certain bin is larger that its successor one. Figure 9 shows that  $B_2$  is missing because the DNL at  $B_1$  is 1 LSB. Figure 9 also shows the non-monotonicity in the transfer characteristic due to negative DNL for couple of the steps.

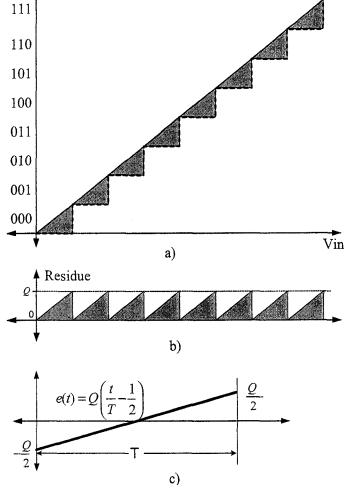

Figure 10 Residue and quantization noise.

#### 2.3.5. SNR, SNDR and ENOB

SNR is the ratio of the *rms* signal amplitude (set at 1 dB below full scale) to the *rms* value of the sum of all other spectral components, excluding the first five harmonics and dc. Alternately, SNR can be calculated as the ratio of the signal power to the total noise power at the output. SNR is usually measured for a sinusoidal input signal [3].

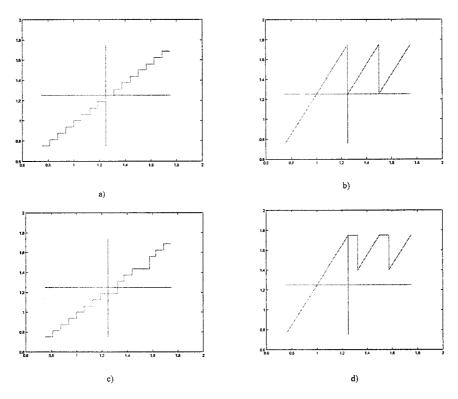

Figure 10 shows the residue of the stages as a function of the input signal. Since the residue is the difference between the input signal and the corresponding quantization level, it is shown as the shaded area in Figure 10.a). Sometimes, the residue plot shown in Figure 10.b) is called the *quantization noise*. The term quantization noise is appropriate since the error that is produced manifests within a system much in the same way as other noise sources [4]. This is especially true when the quantization noise is not correlated with the

input signal. With this assumption in mind and ignoring all other sources of noise in the system, the SNR can be calculated as follows:

$$Q(rms) = \sqrt{\frac{1}{T} \int_{0}^{T} \left( Q\left(\frac{1}{T} - \frac{1}{2}\right) \right)^{2} dt} = \frac{Q}{\sqrt{12}} = \frac{\frac{V_{FS}}{2^{n}}}{\sqrt{12}}$$

(3)

1

$$SNR(dB) = 20\log\left(\frac{V_{FS}(rms)}{Q(rms)}\right) = 20\log\left(\frac{V_{FS}}{2\sqrt{2}}\frac{1}{\frac{V_{FS}}{2^{n}\sqrt{12}}}\right) = 6.02n + 1.76$$

(4)

Where  $V_{FS}$  is the full-scale value of the input signal and n is the nominal resolution of the ADC.

1

The above definition for both SNR and SNDR reflects the way they are measured in the lab, where the *spectral components* and *harmonics* are generated by using the FFT (*Fast Fourier Transform*). Mathematically, SNR is calculated as the difference in dB between the signal rms value and the noise rms value according to the following equation:

$$SNR = signalrms(dB) - noiserms(dB)$$

(5)

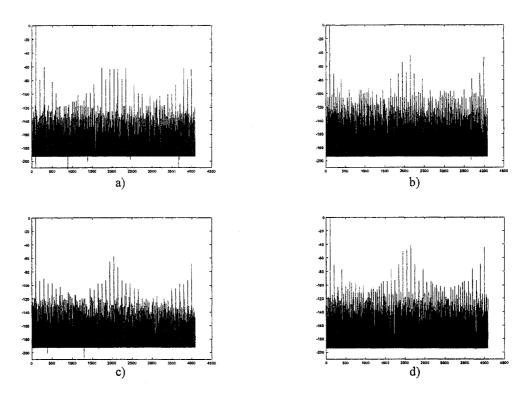

FFT takes a discrete number of time samples, M, and converts them into M/2 discrete spectral components. The spacing between the spectral lines is  $\Delta f = Fs/M$ , where Fs is the sampling frequency. Equation (3) is only valid if the noise is measured over the entire Nyquist bandwidth from DC to Fs/2. If the quantization noise is uncorrelated with the signal, it appears as Gaussian noise spread uniformly over the bandwidth from DC to Fs/2. The FFT acts as a narrowband filter with a bandwidth of  $\Delta f$ , and the FFT noise floor is therefore  $10\log_{10}(M/2)$  dB below the quantization noise level. This is referred to as *processing gain* of the FFT [6].

For example, a 4096 point FFT has a noise floor of 33dB below the theoretical rms quantization noise floor of 74dB for a 12-bit ADC, while the average noise floor is about 74+33 = 107dB below the full scale.

Also, if the signal bandwidth, BW, is less than Fs/2, then the SNR with the signal bandwidth is increased because the amount of quantization noise within the signal bandwidth is smaller [6]. The overall expression of the SNR will be:

$$SNR(dB) = 6.02n + 1.76 + 10 \log_{10}\left(\frac{fs}{2 \cdot BW}\right) + 10 \log_{10}\left(\frac{M}{2}\right)$$

(6)

Another way of calculating the SNR can be achieved by measuring the powers of the signal and the quantization noise in the system.

Effective number of bits (ENOB) is defined by the following equation:

$$ENOB = \frac{SNDR_p - 1.76}{6.02}$$

(7)

Where  $SNDR_P$  is the peak SNDR of the converter expressed in dB.

SNDR is defined to be the ratio, expressed in dB, of the RMS value of the input signal to the RMS value of all of the other spectral components below the Nyquist frequency including harmonics, but excluding DC.

#### 2.3.6. Dynamic Range and SFDR.

Dynamic range is the ratio of the maximum allowable input swing to the minimum input level that can be sampled with specified accuracy [5].

Probably the most significant specification for an ADC used in a communications application is its *Spurious Free Dynamic Range* (SFDR), which is defined as the ratio of the rms signal amplitude to the rms value of the peak spurious spectral component (measured over the entire Nyquist bandwidth) and it may or may not be a harmonic. SFDR is generally plotted as a function of signal amplitude and may be expressed relative to the signal amplitude (dBc) or the ADC full scale (dBFS) [6]. This measurement indicates the amount of dynamic range that can be obtained from the ADC before distortion becomes dominant.

For a signal near full scale, the peak spectral component is generally determined by one of the first few harmonics of the fundamental. However, as the signal falls several dBs below full scale, other components generally occur which are not direct harmonics of the input signal. Therefore, SFDR considers all sources of distortion, regardless of their origin.

#### 2.3.7. Latency

Latency is the time taken by an ADC to generate the digital equivalent of the analog input. It is measured by the number of clock cycles between conversion initiation and the associated output data being made available.

#### 2.3.8. Aperture Jitter

It is the variation in the aperture delay from sample to sample. Aperture jitter shows up as input noise to the ADC.

#### 2.3.9. PSRR (Power Supply Rejection Ratio)

It is the ratio of the change in DC power supply voltage to the resulting change in Full Scale Error, expressed in dB.

#### 2.3.10. THD

Practically, THD is the ratio of the RMS value of the first six harmonic components to the RMS value of the measured input signal and is expressed as a percentage or decibels.

## 2.4. Conclusions

The terminology commonly used in ADCs was presented in this chapter. This terminology is key to the understanding of the specifications of ADCs as well as the measurement of their performance.

#### References

- [1] W. Black, EE501 Course at Iowa State University.

- [2] Engineering Staff at Analog Devices, Analog-Digital Conversion Handbook, Prentice-Hall, Inc. 1986.

- [3] Analog Devices data sheet AD9430.

- [4] M. Koen, "High performance analog to digital converter architectures," Proceedings of the 1989 Bipolar Circuits and Technology Meeting, pp. 35 - 43

- [5] B. Razavi, Principles of Data Conversion System Design, 1995 by AT&T.

- [6] W. Kester, High Speed Design Techniques, Analog Devices, 1996.

## CHAPTER 3. ADC Architectures

#### 3.1. Introduction

ADCs are becoming more and more important with the advancements in the digital processing design. Different systems require different specifications for the ADCs, and many architectures have been implemented to meet those different requirements. Among those requirements are high speed, high resolution, high SNR, low power, low DNL, small latency, small area or any combination of the above. None of the existing architectures meet all of the above requirements, which is expected from engineering sense, and so, the designer of the ADC should be able to pick the architecture that best meets the requirements. Among those architectures that will be discussed in this chapter are: Flash, Half Flash, or Two-step Flash, Multistep, Folding, Folding and Interpolating, Recycling, Successive Approximation, Pipeline and Parallel Pipelined.

#### 3.2. Flash ADCs

The fastest of all types of high-speed analog to digital converters and perhaps the easiest to understand is the flash converter. The flash converter is considered to be the fastest because the conversion takes place in a single cycle, hence the name flash [2]. They have been implemented most commonly in Bipolar IC technology, where the excellent  $V_{BE}$  matching allows design of comparators accurate to 8 bits or better. In MOS technology, calibration cycles are typically required to eliminate comparator offset, which reduces the maximum available clock rate. Speeds up to 2GHz have been achieved [3], and conversion rates of up to 300MHz are readily available on the commercial market. The resolution of a flash converter tends to be limited to 8 bits due to the fact that the amount of circuitry doubles every time the resolution is increased by one bit.

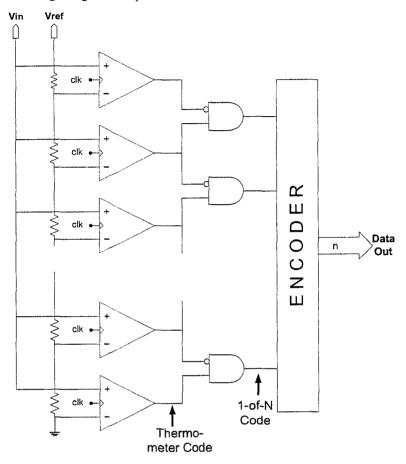

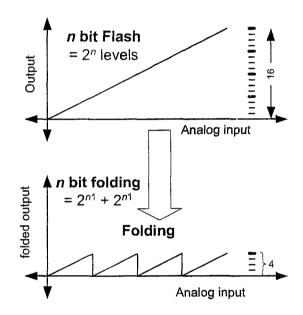

In a flash architecture,  $2^n - 1$  clocked comparators are used to simultaneously compare the input signal with a set of reference voltages generated with a resistor divider, where *n* is the nominal resolution of the ADC [4]. At the output, a so called linear code, or thermometer code, is generated. If a particular comparator's reference point is below the level of the input signal, the comparator's output is high, or ONE, while, if the reference point is above the input, the comparator's output is low, or ZERO. When every thing is ideal, the collection of comparators' outputs should resemble a thermometer; all ZEROs above the input signal level and all ONEs below. The transition from ZERO-block to ONE-block is related to the value of the input signal. The thermometer is then converted to a 1-of-N code, which is subsequently encoded to *n* bits to produce the output

as shown in Figure 11, which shows a block diagram of an n-bit flash ADC. Usually, the encoder shown in the figure is implemented using a large but simple ROM.

Figure 11 Block diagram of an n-bit flash ADC.

The flash structure is a simple one but uses a lot of chip area to implement the block of decision stages as well as the encoding ROM. The large chip area may result in a layout related problems such as skew in the clock signals, buffering of the sampling clock, ..., etc. The large number of comparators gives rise to problems such as dc deviation of the reference voltages generated by the ladder, large *nonlinear* input capacitance, and kickback noise at the analog input. The nonlinear input capacitance will introduce harmonic distortion in the sampled signal. That is mainly due to the fact that the input signal will encounter an amplitude-dependent delay. The kickback noise is the power of the transient noise observed at the comparator input due to switching of the amplifier and the latch. These two effects are explained well in [5]. Under extremely high input slew rate conditions, timing differences between signal paths or even slight differences in comparator response time can cause the effective trip point of one comparator to be different from another. Consequently, a ONE may be found above a ZERO in the thermometer code even though this cannot happen at dc.

Errors of this type are sometimes referred to as "bubbles" because they resemble a bubble in the "mercury" of the thermometer code [6]. Various circuit techniques have been devised to suppress the effect of bubbles. One approach is to use three-input gate, which will require two ZEROs and a ONE in order to indicate a transition. Other approaches to solve this problem include a voting process [6], Gray coding and "quasi-Gray" coding [7]. Another problem that appears in flash ADCs is what is called *metastability*, in which a small difference at the input of a comparator will cause the comparator to take a long time to produce a well-defined logic output.

This small difference occurs when the input signal level is very close to the reference value of a certain comparator and hence, the comparator output may not be a valid output, which will cause erroneous digital output for that particular conversion.

#### 3.2.1. Advantages

The advantages of the flash converter can be summarized in the following points:

- The primary advantage of the flash conversion architecture is its high conversion rate. By pipelining the digital decoding operation, the input signal can be sampled and digitized at the same time the digital circuit is decoding a previous sample of the input signal; therefore, only 2 clock phases are required per conversion, corresponding to the latched and unlatched states of the comparators. The speed of this architecture is therefore only limited by the speed of the comparators and logic.

- If a resistor string divides the reference, the reference exhibits inherent monotonicity; that is, the reference voltage between any point on the string and the end with the lowest voltage is a non-decreasing function of increasing distance between the two points. The transfer curves of resistor string based flash converters can therefore be made monotonic.

#### 3.2.2. Limitations

The main disadvantages of the flash type ADCs are:

- Large silicon area,

- large input capacitance,

- large power dissipation.

Unfortunately, those three issues grow exponentially as the number of bits increases.

#### 3.3. Two-step Flash ADCs

Figure 12 Two-Step flash ADC.

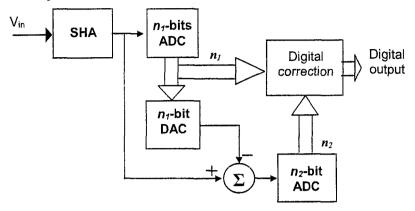

One approach to solve the exponential growth of power, area, and input capacitance of the flash ADC with its nominal resolution is to divide it into two less number of resolution flash ADCs. This architecture is called the *two-step flash ADC*, in which the first step performs a *coarse* conversion, while the second one does a *fine* conversion. For an *n*-bit two-step flash ADC, the first step will resolve  $n_1$  bits, while in the second step,  $n_2$  bits are resolved, where  $n_1$  and  $n_2$  are less than n and  $n_1 + n_2 = n$ .

The two-step flash architecture is an effective means of realizing high-speed, high resolution ADCs because it can be implemented without the need for operational amplifiers having either a high gain or a large output swing. Moreover, with conversion rates approaching half those of fully parallel designs, such half-flash architectures provide both a relatively small input capacitance and low power dissipation [8].

Problems associated with two-step flash ADCs are: poor linearity due to separated two-step comparison, slow-conversion rate, lack of precision and high speed internal sample-and-hold circuitry. Some solutions to the above problems include the implementation of pipelined and multiplexed two-step architecture to improve the conversion rate, while a development of an auto-zeroed differential sample-and-hold comparator will improve precision and speed [9].

The linearity of two-step A/D converters has been limited to a 10-bit level using passive component mismatches. To increase the resolution of the two-step ADC, error correction or calibration techniques have been used. One bit of redundancy, or overlap, can be used between the two stages to enable the second stage to correct for out-of-range errors in the first stage, thereby relaxing the precision required of the first-stage comparators. Furthermore, fully differential architecture increases the input dynamic range, eliminates even-order harmonic distortion, and suppresses common-mode noise due to supply transients and substrate coupling. Other techniques include a *direct code-error calibration* in the digital domain has been used by [10] to improve the linearity. This technique reduces feedthrough, offset and interstage gain errors simultaneously.

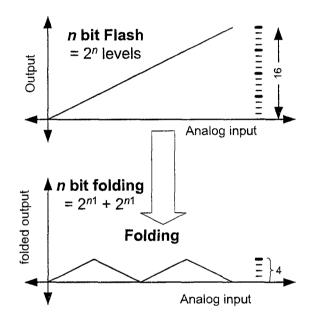

#### 3.4. Folding ADCs

For resolution around 8 bit, flash ADC is the fastest possible architecture. The sampling speed of the flash converter is limited to the maximum speed of a comparator in that technology. On the other hand, the major disadvantage of the flash ADC is the exponential dependency of several of its parameters such as power consumption, area, and input capacitance [11].

A *folding* architecture can be considered as a continuous-time two-step architecture. In a two-step ADC converter, the signal conversion is split into two or more phases in time. The two stages work in tandem, where the second stage waits for the first stage to finish processing and pass the residue, and then it starts the quantization process.

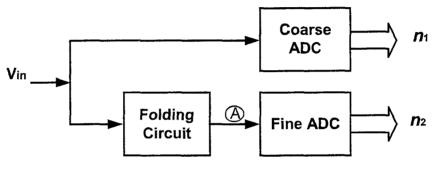

Figure 13 Block diagram of a folding ADC.

In folding ADC, signal conversion consists of a coarse and fine conversion stages, but those conversions are done in parallel. This gives the folding ADC the same maximum clock frequency that can be achieved with full-flash ADC with a power and area comparable to that of a two-step ADC. Figure 13 shows the block diagram of a folding ADC.

Figure 13 shows that the input signal is applied to two paths at the same time. The first path includes the coarse ADC that resolves the MSBs of the signal. In other words, if the coarse ADC is a 3-bit one, for example, it tells which octant, (1/8 of the whole range), of the input range the input signal lies. The second path does two operations on the signal. The first operation is what is known as *folding* the signal, while the second is a regular quantization process.

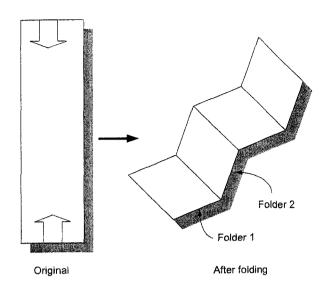

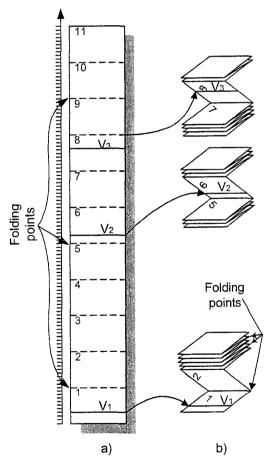

The folding operation is illustrated in Figure 14 and Figure 15. Figure 14 shows the folding operation where a piece of paper is folded into 4 folders. In Figure 15.a), another piece of sheet is folded into 11 smaller folders as numbered in the figure. The smaller folders are identical in their length, which is shown as height in Figure 15.a). The folding points, which are the points where the original sheet is going to be folded, are shown as dotted lines in the original sheet. There are three points on the original sheet; V1, V2 and V3, shown as solid lines. Those three points are mapped to their location after folding as shown in Figure 15.b).

Figure 14 Folding operation.

Figure 15 Folding operation; mapping of signal values.

The main function of the folding circuit is to map an input value, such as V1 or V2 to its place in one folder, while making the other folders transparent. This operation is similar to opening only one folder that contain the original value, while stacking the other folders over each others as shown in Figure 15.b).

The *folding factor* is the number of folds the input signal experiences. For example, a *folding factor* of 4 means that the signal is folded into 4 folds or folders.

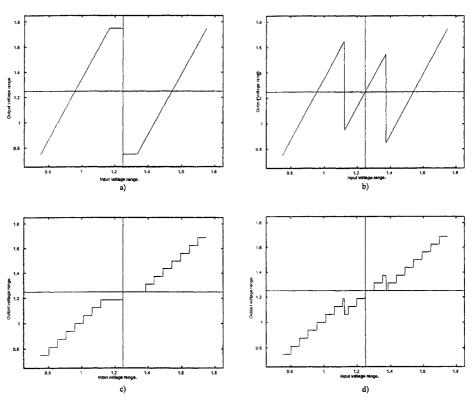

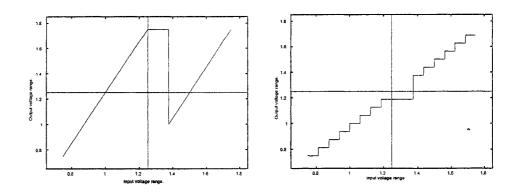

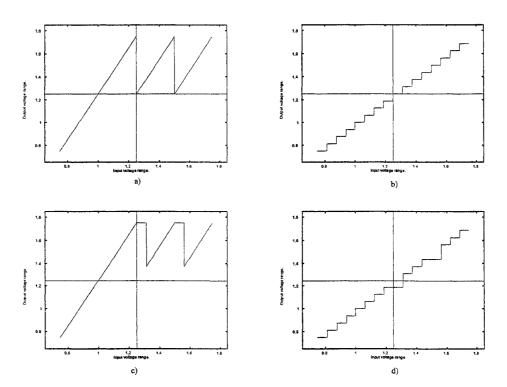

A folder circuit can fold the input signal to a sawtooth waveform, as shown in Figure 16 or to a triangular waveform as shown in Figure 17. The folding factor in both figures is 4.

A mathematical model for the folding circuit is a useful tool in order to understand and imagine how the input waveform shown in Figure 15 will be at point A as a function of time, t, in the same figure after the folding circuit.

Figure 16 Output of the folder circuit as a sawtooth waveform.

The output of a folding circuit that generate a sawtooth waveform can be modeled mathematically as:

$$V_{A}(t) = \left(\frac{V_{in}(t)}{A} \times n - \left\lfloor \frac{V_{in}(t)}{A} \times n \right\rfloor\right) \times \frac{A}{n}$$

(1)

Where A is the amplitude of the input signal,  $V_{in}(t)$ , and n is the folding factor.

The output of a folding circuit that generate a triangular waveform can be modeled mathematically as:

$$i = V_{in}(t) \times \frac{n}{A}$$

<sup>(2)</sup>

$$V_A(t) = \frac{\left(1 - \left(-1\right)^i\right)}{2} \times \frac{A}{n} + \left(-1\right)^i \times \left(V_{in}(t) \times \frac{n}{A} - i\right) \times \frac{A}{n}$$

(3)

Where A is the amplitude of the input signal,  $V_{in}(t)$ , and n is the folding factor.

The input signal is applied to the folding circuit and the output of this circuit is then passed to the fine ADC. At the same time, the input signal is connected to the coarse ADC. The operation of the folding circuit is illustrated in Figure 17. The "zig-zag" shaped transfer curve covers the whole  $V_{in}$  range, and the output signal of the folding circuit needs to be converted to only  $2^{n_2}$  levels corresponding to the  $n_2$  least significant bits of the ADC converter output code [12].

Figure 17 Output of the folder circuit as a triangular waveform.

A track-and-hold amplifier is not necessary in a folding ADC. However, the input signal frequency is multiplied in the folding circuit as a result of the *folding* operation. The maximum frequency multiplication in a folding system is determined by the *folding factor* of the ADC. A high folding factor results in a low number of comparators, but on the contrary, it lowers the maximum signal frequency of the ADC. A track-and-hold circuit might be used to overcome this bandwidth limitation [13].

### 3.5. Multistep ADCs

A multistep ADC architecture extends the concept of two step ADC to many stages. The total number of comparators in this ADC will be less than that of a two-step flash, but that will be on the expense of the conversion time, which will be reflected on the overall speed of the ADC.

# 3.6. Successive Approximation and Algorithmic converters ADCs

Both the successive approximation and algorithmic ADC topologies requires N clock cycles to perform an N-bit conversion. They both perform one bit of conversion per clock cycle. The successive approximation converter is a subclass of the subranging converter, in which, during each clock cycle only one bit of resolution is generated. The algorithmic converter is a variation of the pipelined converter, in which the pipeline is folded back into a loop. Both topologies essentially perform a binary search to generate the digital value, however, in the case of the successive approximation converter the binary search is performed on the reference voltage, while in the case of the algorithmic converter the search is performed on the input signal.

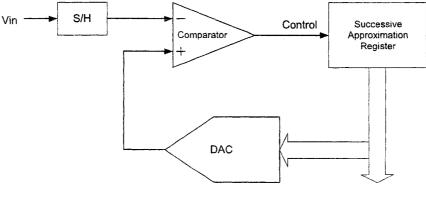

### 3.6.1. Successive Approximation ADCs

A block diagram of the successive approximation converter is shown in Figure 18. Because the conversion requires N clock cycles, a S/H version of the input signal is provided to the negative input of the comparator. The comparator controls the digital logic circuit that performs the binary search. This logic circuit is called the successive approximation register (SAR). The output of the SAR is used to drive the DAC that is connected to the positive input of the comparator.

The operation of the successive approximation ADC is described as follows: During the first clock period, the input is compared to the MSB, i.e., the MSB is temporarily raised high. If the output of the comparator remains high, then the input occurs somewhere between 0 and  $V_{ref}/2$ , and the MSB is reset to 0. However, if the comparator output is low, then the input signal is somewhere between  $V_{ref}/2$  and  $V_{ref}$  and the MSB is set to high. During the next clock, the MSB-1 bit is evaluated in the same manner. This procedure is repeated such that at the end of the N clock periods, all N bits have been resolved [16].

N-bit output

Figure 18 Successive approximation converter block diagram.

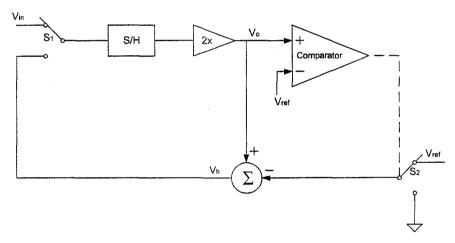

### 3.6.2. Algorithmic Converters ADCs

The algorithmic converter is formed by one stage that evaluates all of the N bits. This stage is configured as a loop that requires N clock cycles to finish the evaluation. A block diagram of this converter is shown in Figure 19 and consists of a S/H at the front, an amplifier that multiplies the input by 2, a comparator, and reference subtraction circuit. The operation of the circuit is as follows: The input is first sampled and held by setting  $S_1$  to  $V_{in}$ , the signal is then multiplied by 2. The result of this multiplication,  $V_o$ , is compared to  $V_{ref}$ . If  $V_{on} > V_{ref}$  then the most significant bit,  $b_N$ , is set to 1 or, otherwise, it is set to 0. In the next clock cycle,  $S_1$  is switched to  $V_b$  while  $S_2$  is connected to either  $V_{ref}$  or ground if  $b_N$  is equal to 1 or 0, respectively, such that:

$$V_{bN} = 2V_oN - b_N V_{ref} \qquad b_N = \{0, I\}$$

(4)

This voltage is then sampled-and-held and used to evaluate the MSB-1 bit. This procedure continues until all N-bits are resolved. The general expression for  $V_o$  is given by:

$$Vo_{i} = [2Vo_{i-1} - b_{i} V_{ref}] z^{-1}$$

(5)

where  $b_i$  is the comparator output for the *i*th evaluation and  $z^{-1}$  implies a delay of one clock period

Figure 19 Block diagram of an algorithmic ADC.

## 3.7. Pipeline ADCs

[16].

*Pipelining* is an implementation technique whereby multiple operations are overlapped in execution. Today, fast CPUs in particular and digital systems in general are mainly attributed to pipelining.

A pipeline is like an assembly line. In an automobile assembly line, there are many steps, each is contributing something to the construction of the car. Each step operates in parallel with the other steps, though on a different car. A pipeline ADC consists of many *stages* that are usually, but not necessarily, identical. The stages are connected one to the next to form a pipeline. In most of the implementations, the pipeline is preceded by a circuit, called *Sample-and-Hold* (S/H), used to quantize the input of the pipeline, which is an analog signal.

Each stage does some kind of processing on the input signal and then passes a new signal to the next stage. The main function of each stage is to give some information about the input signal to that stage. Each stage quantizes the input signal to a certain value, or *bin*. The Pipelined ADC (PADC) is very similar to the multistage ADC, while the main difference between them is that PADC has S/H circuits between the stages. Each stage consumes one clock cycle to do the operation and all the stages are working at the same time, but each operates on a different sample of the input signal. More detailed description about the pipeline architecture will be presented in chapter 4.

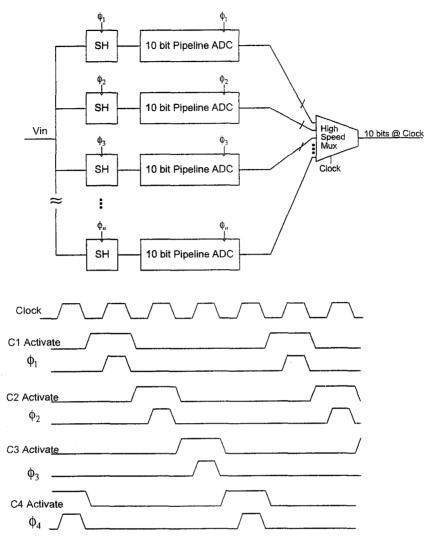

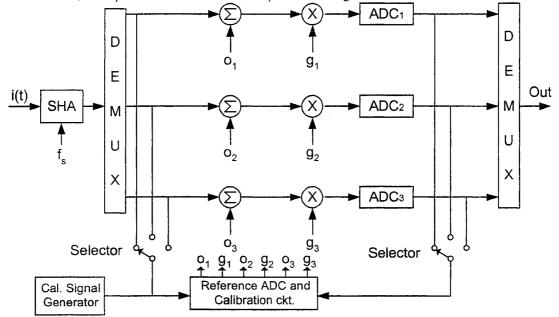

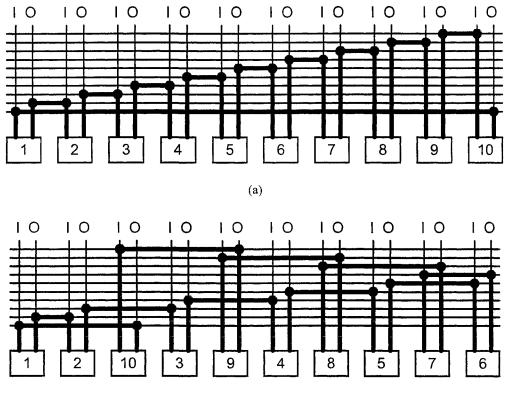

### 3.8. Parallel Pipeline ADCs

Parallel pipeline, or sometimes called as *time-interleaved* pipeline ADCs, are used to increase the speed of the ADC beyond the technological limit. This parallelism can be achieved by connecting multiple ADCs in parallel, and work in a time-interleaved fashion. Time-interleaving means that a sampled version of the input signal is sent first to a first ADC which will start processing it, and then another sample is sent to a second ADC, which will start processing it, and then a third sample is sent to a third ADC, ..., etc, and then a sampled version of the input is sent to the first ADC and so on. Theoretically speaking, the speed of a time-interleaved ADC increases linearly with the increase of the number of the ADCs connected in parallel.

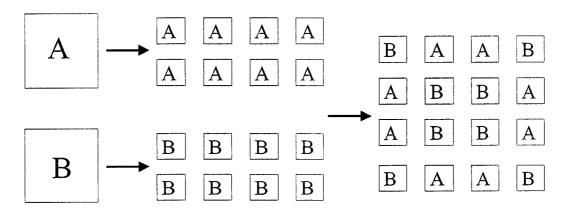

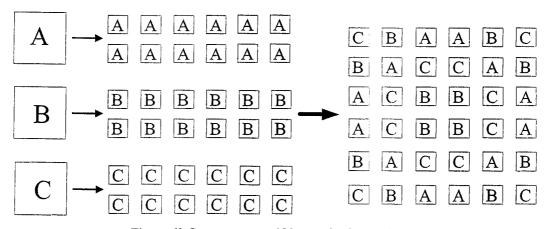

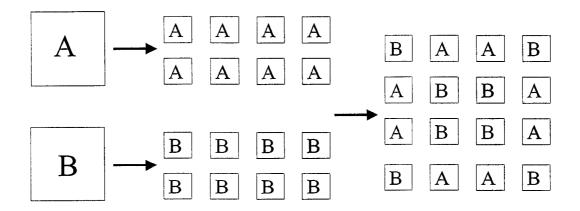

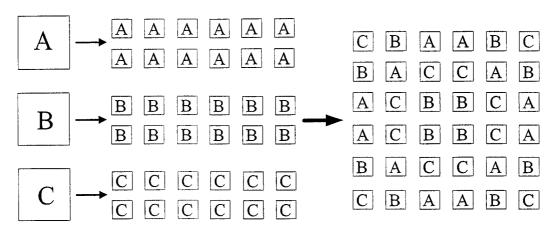

There are different configurations to implement the parallel ADC[17][18][19]. Each one of the ADCs in the parallel ADC can be of any type, however, the most common in the market are successive approximation ADCs, pipeline ADCs or sigma-delta ADCs. Figure 20 shows a parallel pipeline ADC that consists of M=4 pipeline channels or paths. Assuming that the overall ADC operates at a sampling frequency  $f_s$ , each ADC operates at a sampling rate of  $f_s/M$ . A major advantage of this approach is that a considerable saving in the silicon area can be achieved compared to other architectures with the same specifications. Although this architecture will, in some cases, result in increased noise or distortion, however, these effects are both predictable and consistent, and may be minimized in the design of an array of parallel ADCs[17].

Because of the time uncertainty (jitter) of the sample-and-hold circuit preceding each ADC in the array when switching from the sampling to the holding mode, a very accurate analog demultiplexer is needed at its input in order to convert a single high-speed signal into M lower speed analog sampled-and-held signals. Another problem with this architecture arises if mismatches occur among the channels creating aliasing and distortion in the resulting digital output [19]. Such kind of errors in the parallel architecture will be analyzed in chapter 4 in more details.

Figure 20 Parallel-pipeline ADC in time-interleaved fashion.

# 3.9. Oversampling ADCs

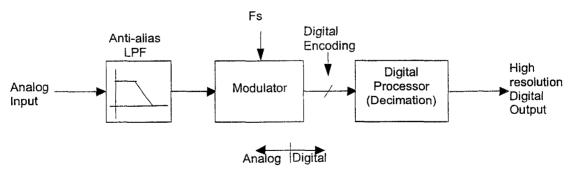

Figure 21 Block diagram for a 1-bit oversampled ADC.

Oversampling A/D converters modulate their analog inputs into short digital words at very high sampling rate. A special kind of filters, called *decimation filters*, resample this code at the Nyquist<sup>1</sup> rate of the signal and increase the word length to maintain resolution.

Sigma-delta,  $(\Sigma\Delta)$ , modulation has been the preferred technique for oversampling conversion and they have been widely used in applications where high accuracy analog circuitry would otherwise be required. Oversampling converters use simple and relatively high tolerance analog components but require fast and complex digital signal processing stages. Recent experience with oversampling converters has shown that their circuits can be designed and scheduled with more assurance than had been possible with the more analogintensive techniques [14].

#### 3.9.1. Sigma Delta Modulation

A generalized oversampled ADC systems is shown in Figure 21. The block diagram of the oversampled converter shows three main system blocks: the anti-aliasing filter, the analog modulator and digital decimator.

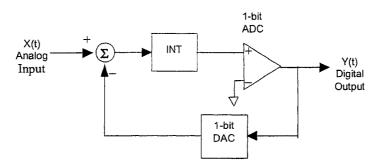

Oversampling ADCs converters achieve high resolution by shifting their quantization noise outside the signal band and then removing it with digital filters. The process that shapes the quantization noise in the sigma-delta modulator that is shown in Figure 22 can be explained as making a prediction of low frequency values of the noise and subtracting it from the signal.

This prediction process works well when its sampling frequency is high with respect to the Nyquist rate, which will result in ADCs with fine resolution. This resolution also improves with the number of levels in the internal quantizer and with the order of the prediction. Very reliable modulators have been built having just two-level quantization and second order prediction.

The major advantage of oversampled ADC system is that the analog circuit complexity can be greatly reduced if the encoding is selected such that the modulator only needs to resolve a coarse quantization (frequently a single bit). Also, if oversampling rates are high, the baseband is a small portion of the sampling frequency. Consequently, constraints on the analog anti-aliasing filter can be relaxed, permitting gradual roll-off, linear phase and easy construction with passive components [15].

Figure 22 illustrates the simplest form of an oversampled interpolative modulator, which features an integrator, a 1-bit ADC and a DAC, and a summer. This topology, known as sigma-delta, uses feedback to lock onto a band-limited input X(t).

<sup>&</sup>lt;sup>1</sup> Nyquist rate is half the input signal frequency. For example, if the input signal is running at a 10MHz frequency, then its Nyquist rate is 5MHz.

Figure 22 Block diagram of 1-bit Sigma-Delta loop.

Unless the input X(t) exactly equals one of the discrete DAC output levels, a tracking error results. The integrator accumulates the tracking error over time and the in-loop ADC feeds back a value that will minimize the accumulated tracking error. Thus, the DAC output toggles about the input X(t) so that the average DAC output is approximately equal to the average of the input.

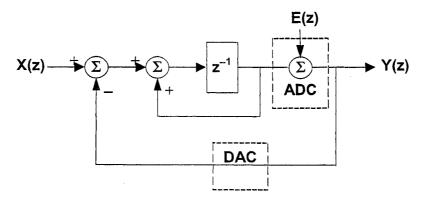

The operation of the sigma- delta modulator can be analyzed quantitatively by modeling the integrator with its discrete-time equivalent and the quantization process by an additive noise source as illustrated in Figure 23.

Figure 23 Discrete time equivalent of delta-sigma loop.

### 3.10. Conclusions

In this chapter, the common architectures of ADCs were presented. Each one of those ADCs has its own characteristics that makes it fit in a certain application. The specifications of those ADCs are always trading with each other. The higher the speed is, the lower the resolution is, and the more the power is. High speed ADCs are always low resolution, while high resolution ADCs are always low speed ones. The designer needs to choose the architecture that best fits its target application.

In a range of Low, Moderate and High, the flash ADC can be described as High speed, High power, Large Area and Low resolution. Two step flash ADCs are Moderate speed, Moderate power, Moderate area and Moderate resolution. The folding ADCs, multistep ADCs and pipeline ADCs are similar to the two step flash classification although they are not exactly identical. Successive approximation and algorithmic ADCs as well as oversampling ADCs are considered High resolution, Low power, area and speed. Although the multipath ADCs are considered High speed, power and area and Moderate resolution, however, they can't achieve the speed of the flash ADCs.

#### References

- M. Koen, "High performance analog to digital converter architectures," Bipolar Circuits and Technology Meeting, 1989., Proceedings of the 1989, pp. 35 - 43.

- [2] K. Balasubramanian, "A flash ADC with reduced complexity," *IEEE Transactions on Industrial Electronics*, Vol. 42, NO. 1, February 1995, pp. 106-108.

- [3] T. Wakimoto, Y. Akazawa, and S. Konaka, "Si bipolar 2-GHz 6-bit flash A/D conversion LSI," IEEE Journal of Solid-State Circuits, VOL. 23, NO. 6, DECEMBER 1988, pp. 1345-1350.

- [4] J. Corcoran, "High speed sample and hold and analog-to-digital- converter circuits," from the book Analog Circuit Design edit by J. H. Huijsing et. al., 1993, Kluwer Academic Publishers.

- [5] R. Razavi, Principles of Data Conversion System Design, 1995, by AT&T, IEEE press.

- [6] C. Mangelsdorf, "A 400-MHz input flash converter with error correction," *IEEE Journal of Solid-State Circuits*, VOL. 25, NO. 1, February 1990.

- [7] Y. Akazawa et al., "A 400 Msps 8b flash AD conversion LSI," in *ISSCC Dig. Tech. Papers*, vol. 30, 1987, pp. 98-99.

- [8] B. Razavi and B. Wooley, "A 12-b 5-Msample/s two-step CMOS A/D converter," IEEE Journal of Solid-State Circuits, VOL. 27, NO. 12, December, 1992, pp. 1667-1678.

- [9] T. Matsuura, T. Tsukada and S. Ohiba, "An 8b 20MHz CMOS half-flash A/D converter," IEEE ISSCC 1988, pp. 220-221.

- [10] H. Lee and B. Song, "A code-error calibrated two-step A/D converter," IEEE ISSCC 1992, pp. 38-39.

- [11] R. Roovers and M. Steyaert, "Design of CMOS A/D converters with folding and/or interpolating techniques," Advanced A-D and D-A Conversion Techniques and their Applications, 6-8 July 1994, Conference Publication No. 393, pp. 76-81.

- [12] B. Nauta and A. Venes, "A 70-MS/s 110-mW 8-b CMOS folding and Interpolating A/D converter," IEEE Journal of Solid-State Circuits, VOL. 30, NO. 12, December 1995, pp. 1302-1308.

- [13] A. Venes and R. Plassche, "An 80-MHz, 80-mW, 8-b CMOS folding A/D converter with distributed trackand-hold preprocessing," *IEEE Journal of Solid-State Circuits*, VOL. 31, NO. 12, December 1996, pp. 1846-1853.

- [14] G. Temes and J. Candy, "A tutorial discussion of the oversampling method for A/D and D/A conversion," *IEEE 1990*.

- [15] S. Nadeem and C. Sodini, "Oversampled Analog-to-Digital Converters," Analog Circuit Design, edited by J. Huijsing et al., Kluwer Academic Publishers1993.

- [16] Ramesh Harjani, Analog-to-Digital Converters, The Circuits and Filters Handbook, *IEEE Press*, pp 2098-2127, 1995.

- [17] W. C. Black, Jr. and D. A. Hodges, "Time interleaved converter arrays," *IEEE J. Solid-State Circuits*, vol. SC-15, pp. 1022-1029, Dec. 1980.

- [18] C. S. G. Conroy, D. W. Cline, and P. R. Gray, "An 8-b 85-MS/s parallel pipeline A/D converter in 1-um CMOS," *IEEE J. Solid-State Circuits*, vol. 28, pp. 447-454, Apr. 1993.

- [19] A. Petraglia and S. K. Mitra, "Analysis of mismatch effects among A/D converters in a time-interleaved waveform digitizer," *IEEE Trans. Instrum. Meas.*, vol. 40, pp. 831-835, Oct. 1991.

# **CHAPTER 4.** Pipeline ADCs

### 4.1. Introduction

Pipelining is an implementation technique whereby multiple operations are overlapped in execution. Today, fast CPUs in particular and digital systems in general are mainly attributed to pipelining.

A pipeline is like an assembly line. In an automobile assembly line, there are many steps, each contributing something to the construction of the car. Each step operates in parallel with the other steps, though on a different car. A pipeline ADC, (PADC), consists of many stages, that are usually, but not necessarily, identical. The stages are connected one to the next to form a pipeline. In most of the implementations, the pipeline is preceded by a circuit, called Sample-and-Hold (S/H), used to quantize the input to the pipeline, which is an analog signal.

Each stage does some kind of processing on the input signal and then passes a new signal to the next stage. The main function of each stage is to give some information about the input signal to that stage. Each stage quantizes the input signal to a certain value, or bin. The Pipelined ADC is very similar to the multistage ADC, while the main difference between them is that pipeline ADC has S/H circuits between the stages. Each stage consumes one clock cycle to do the operation and all the stages are working at the same time, but each operates on a different sample of the input signal.

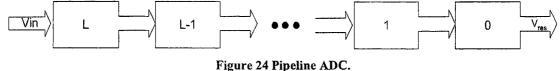

A block diagram that shows the operation of the pipeline ADC is shown in Figure 24.

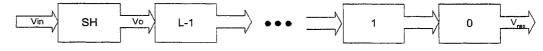

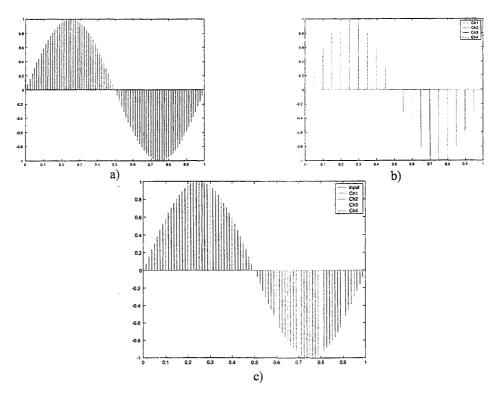

Usually, the first stage of a pipeline ADC is the S/H as shown in Figure 25. The main function of the S/H is to generate an output same as the input signal but at specified times. Figure 26 shows a sinusoidal input signal as the input to the pipeline, Vin and the sampled output, Vo.

Figure 25 Pipeline ADC with SH.

The main operations done by each stage are:

- giving information about the input signal in form of a digital number,

- amplifying, and,

- bounding the signal.

Usually, the last two operations are done together to insure that the next stage in the pipeline will be able to work on the signal passed to it from the current stage. This operation is done by subtracting a specific value from the input signal such that the result is within the range that the next stage can handle. This is called the *input range* of the next stage. A single stage of the PADC is shown in Figure 27.

Figure 26 Input and output of the SH stage.

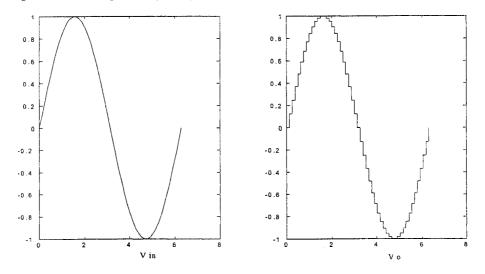

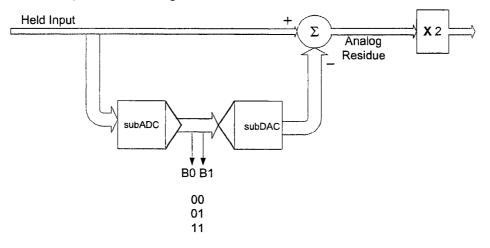

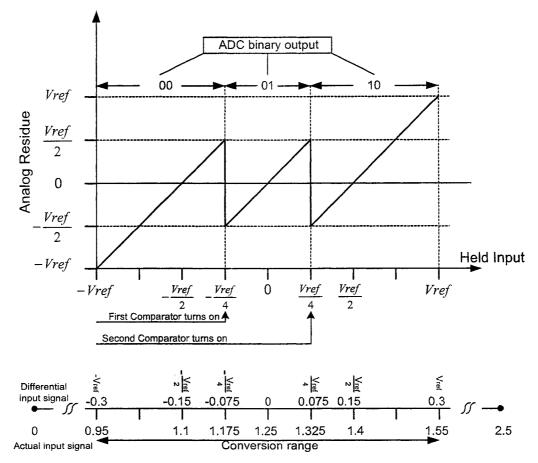

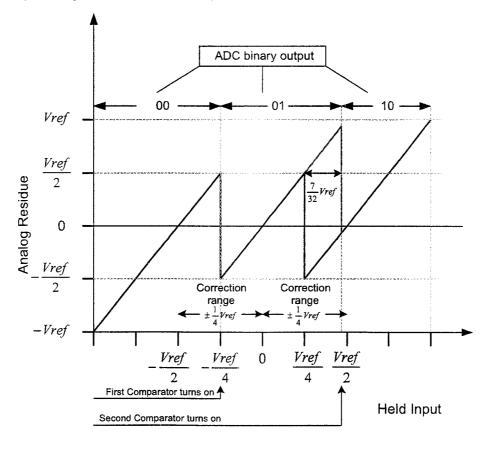

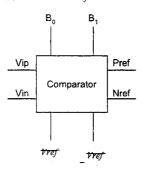

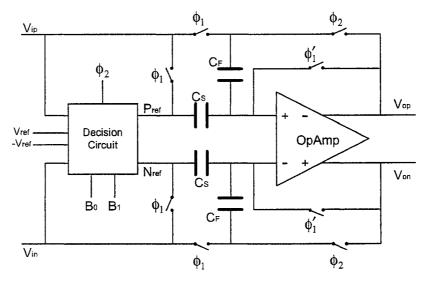

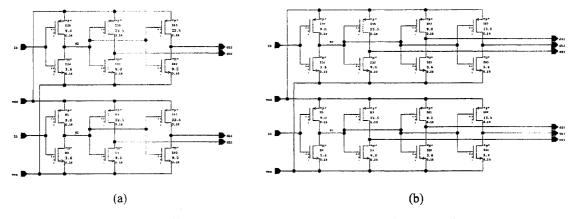

Each stage of the ADC consists of a subADC, subDAC and a subtractor. The subADC is an ADC that generates smaller number of bits than the original ADC. In this design, each subADC generates 1.5 bits and contains two comparators. It is a small flash ADC. The subDAC is a small DAC that takes the output of the subADC to generate an analog output to be used in the subtractor.

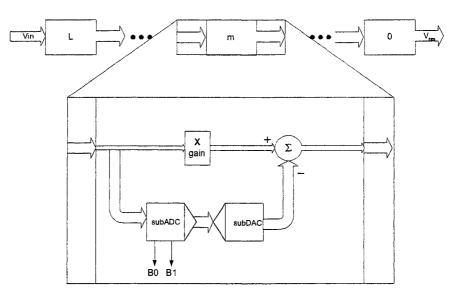

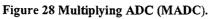

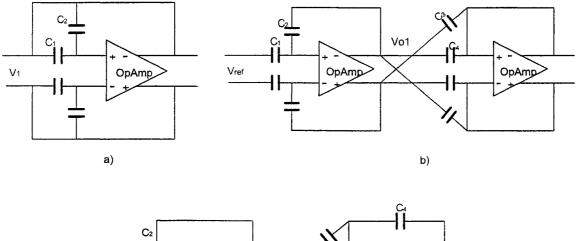

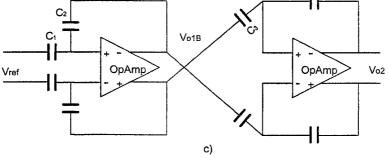

Fortunately, all these operations can be done in one circuit called the multiplying ADC, (MADC), [1]. This circuit is shown in Figure 28, where the subADC consists of the switching circuit that contains the comparators and some logic circuits and the subDAC and the subtractor are made of the switches, reference voltages and the operational amplifier.

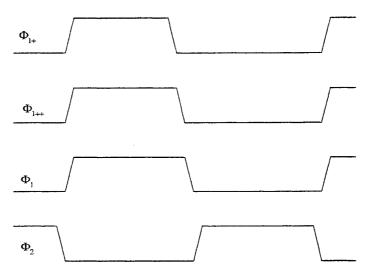

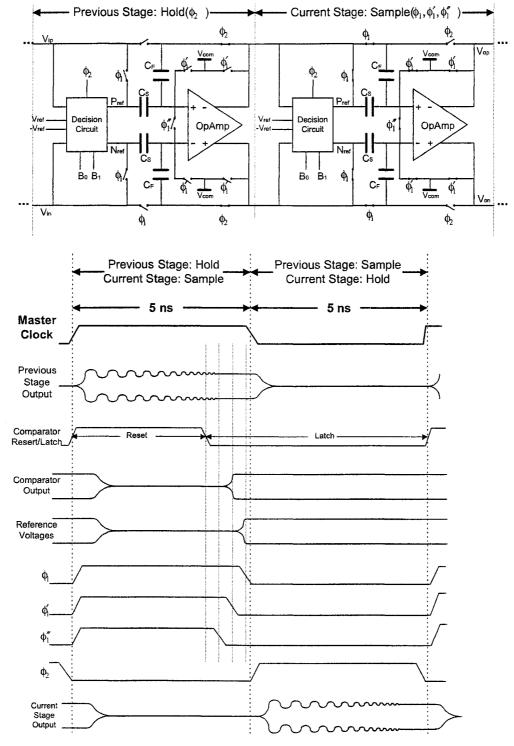

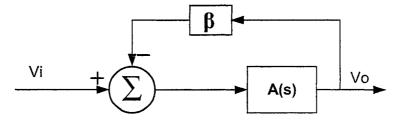

The clocking scheme used to operate the operational amplifier circuit shown in Figure 28 is shown in Figure 31. This configuration has been chosen because it has smaller feedback ratio,  $\beta$ , than other configurations with the same closed loop gain. The smaller  $\beta$  means the faster the opamp to settle to its final value. A second advantage to this configuration, as will be shown later, is that it is less sensitive to capacitor mismatch, which means more accurate closed loop gain.

Figure 27 One stage of the PADC.

The switches shown in Figure 28 can be either a simple NMOS or PMOS transistor or a transmission gate that includes both. Usually, if a transistor is the choice for a switch, it is chosen to be NMOS, since it is stronger than the PMOS. However, simple transistor realization cannot be used as a switch if the input to that switch is varying too much. The reason is that a single transistor needs to have a sufficient excess bias voltage,  $V_{EB}$ , that will drive its gate. The overdrive voltage is defined to be:

$$V_{EB} = V_{gs} - V_t \tag{1}$$

Where  $V_{gs}$  is the gate-to-source voltage and  $V_i$  is the threshold voltage of the transistor.

The source voltage is going to be the input voltage. If the input voltage gets close to the gate voltage, then  $V_{gs}$  is very small and might be less than  $V_t$  and so, the transistor will not have enough overdrive voltage to able to turn it ON or OFF.

To overcome this problem, there are two choices available in literature.

1) Use a clock-boosting scheme [2].

2) Use a transmission gate switch.

The first choice has some disadvantages and mainly used in low voltage applications.

Usually, switches that are connected to the input voltage in Figure 28 are realized using a transmission gate. Whether we use a simple transistor or a transmission gate, the overdrive voltage will still be dependent on the input voltage, although, this dependency is less for a transmission gate switch. This will result in input dependent switching.

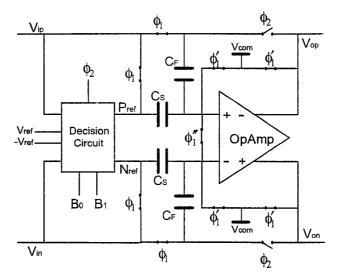

To reduce this phenomenon, a special switching behavior is followed. This is depicted in Figure 28 and Figure 31. Two more clocks;  $\phi'_1$  and  $\phi''_1$  are used to help in reducing the input dependent switching phenomenon. The operation of this switching will be described along with the explanation of the operation of the MDAC.

The operation of the MADC is described next along with Figure 31 that shows the non overlapping clocks used to drive the MADC switches.

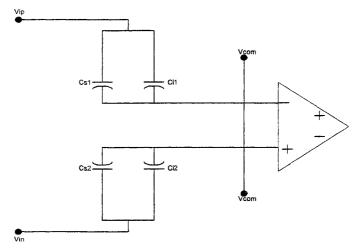

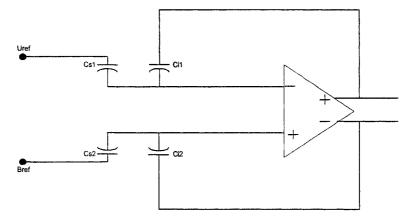

This configuration has been used in [1]. Note that there are 4 capacitors; two of them are called the *sampling* capacitors and the other two are called the *integrating* capacitors. Two of the 4 capacitors; one sampling and another integrating, are connected to the positive side of the opamp, while the other two are connected to the negative side of the opamp. The bottom plates of the sampling and integrating capacitors are connected to the summing nodes of the opamp.

Let's consider the capacitors connected to the negative summing node of the opamp: the sampling capacitor  $C_{sI}$  and the integrating capacitor  $C_{iI}$ . There are 4 clocks that control the operation of the circuit:  $\phi_1$ ,  $\dot{\phi_1}$  and  $\dot{\phi_1}$  and  $\dot{\phi_1}$  and  $\dot{\phi_1}$  and  $\dot{\phi_1}$  are identical except that  $\dot{\phi_1}$  goes down first, and then followed by  $\dot{\phi_1}$  and then  $\phi_1$  as shown in the Figure 31.  $\phi_2$  is the nonoverlapping complement of  $\phi_1$  clock.

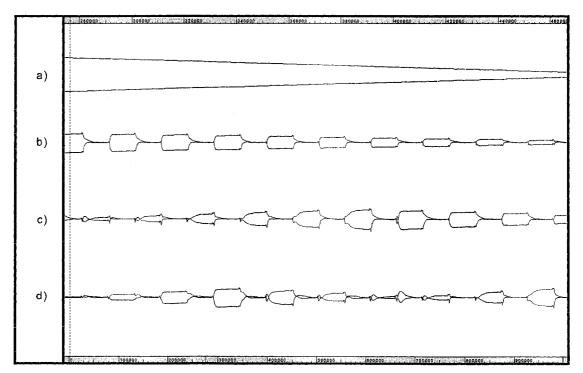

This circuit has a reference clock as its input. A clock generator circuit generates the above 4 clocks and their CMOS complements. As  $\phi_1$  goes into one period, i.e., goes High and then Low, this circuit will go through two modes; *tracking* mode in which the circuit is tracking the input signals on both  $V_{ip}$  and  $V_{in}$ , and *holding* mode, in which the circuit will hold to a constant value. When the circuit changes from the tracking mode to the holding mode, the circuit is said to be sampling the input signal and the held value is going to represent the signal that is being sampled at this moment. The tracking mode occurs while  $\phi_1$  is High. At the same time  $\phi_1$  is High,  $\phi'_1$  and  $\phi''_1$  are also High. The circuit will stay in the tracking mode until  $\phi'_1$  goes Low first, followed by  $\phi''_1$  and then  $\phi_1$ , which will signal the end of the tracking mode. In this mode, the top plates of  $C_{sJ}$  and  $C_{iJ}$  are connected to the positive input,  $V_{ip}$ , while the top plates of  $C_{s2}$  and  $C_{i2}$  are connected to the negative input,  $V_{in}$ . At the same time the bottom plates of all capacitors are connected together and to the common mode voltage. This is shown in Figure 29.

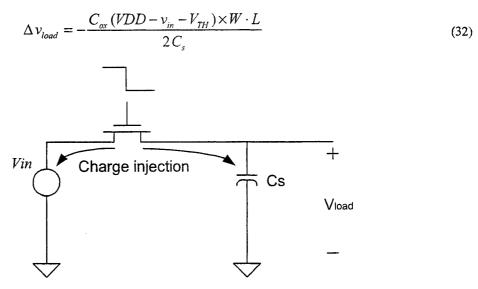

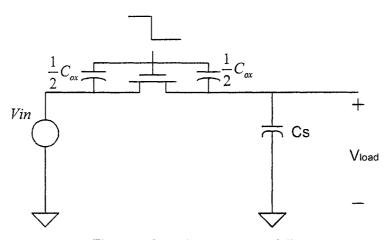

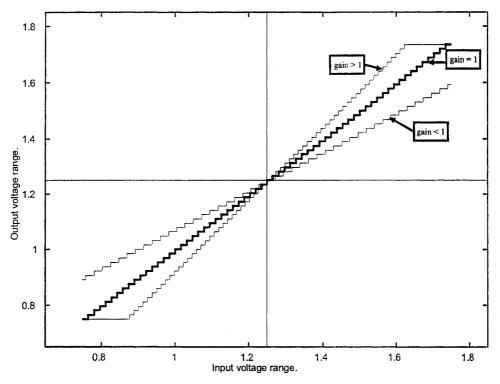

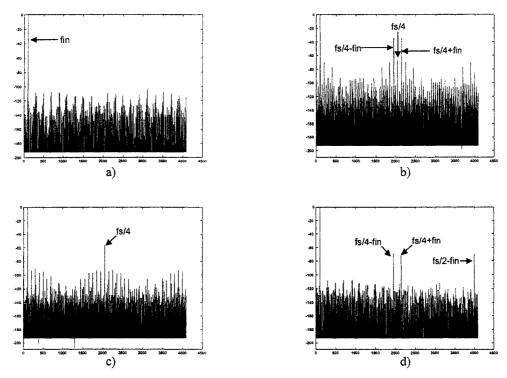

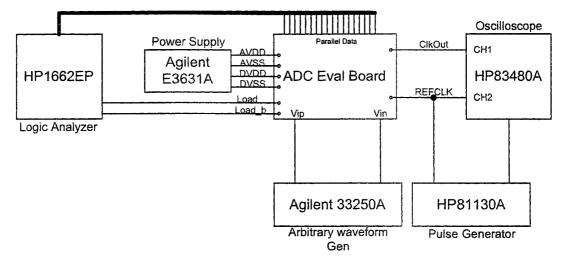

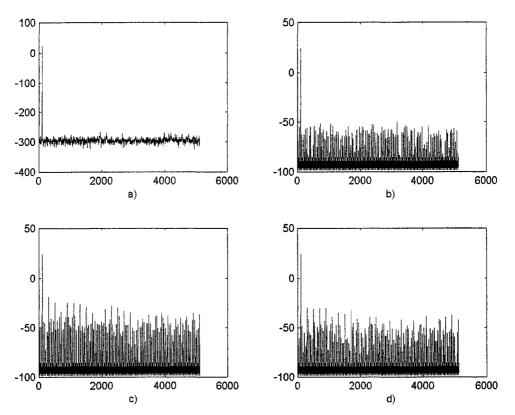

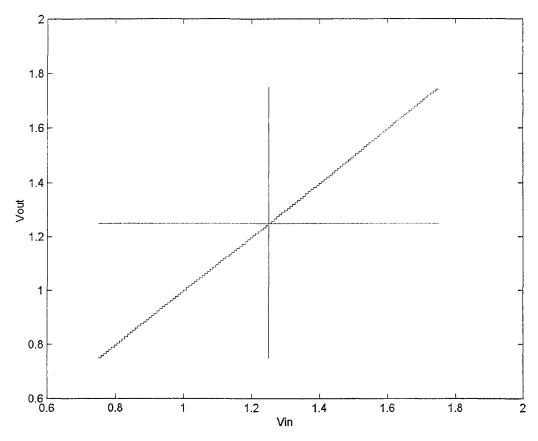

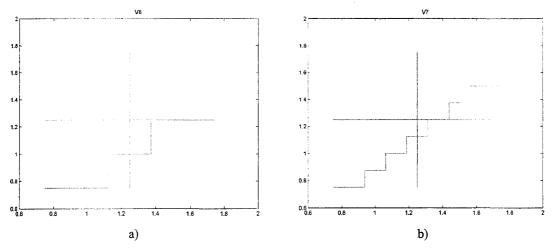

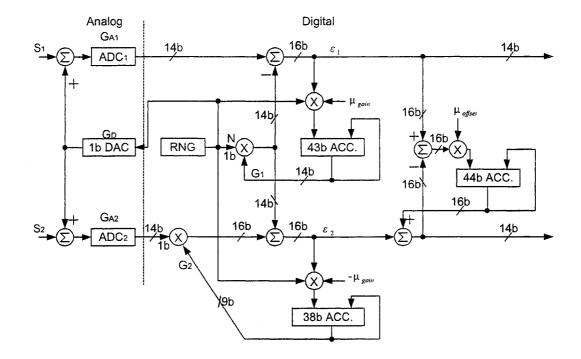

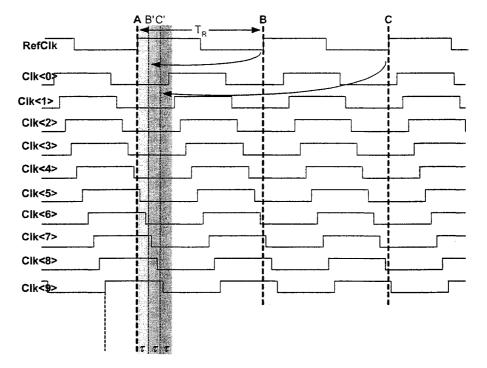

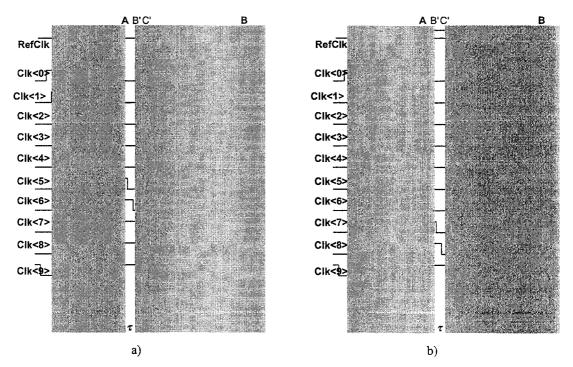

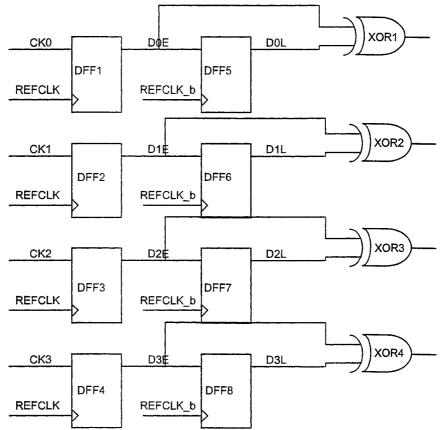

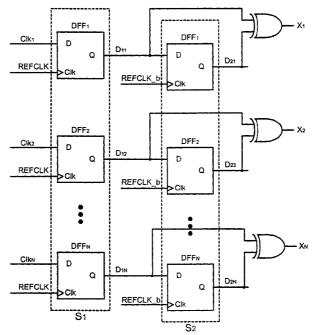

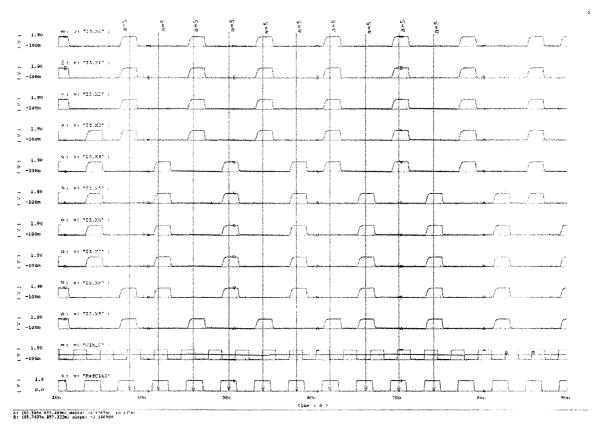

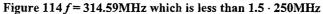

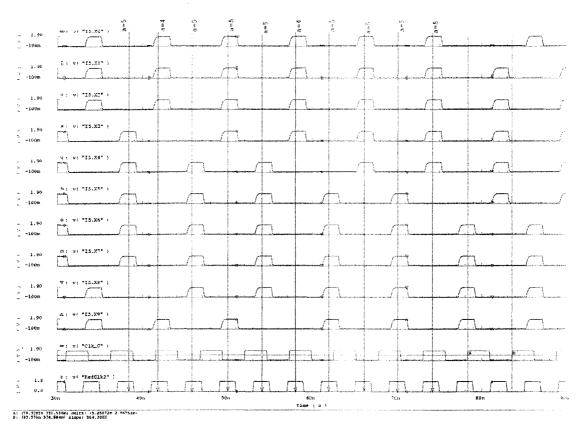

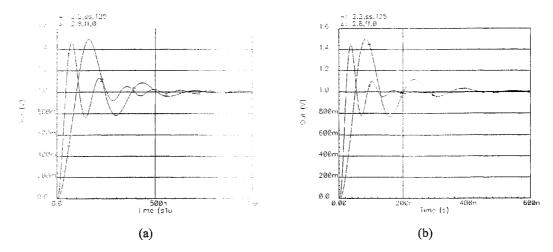

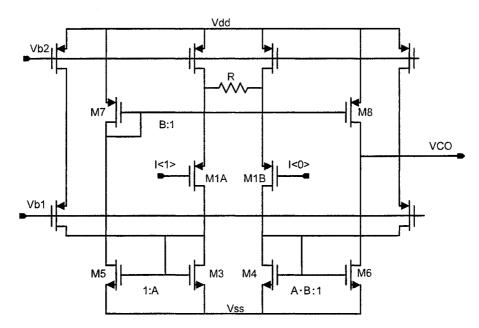

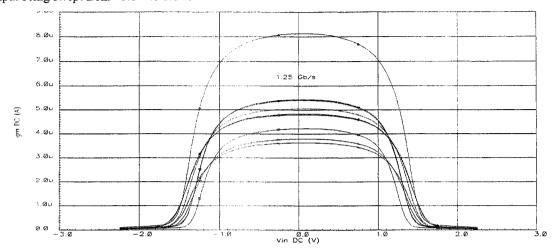

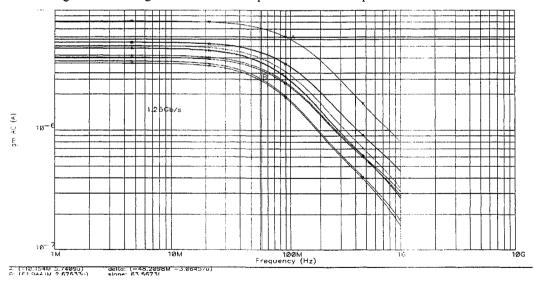

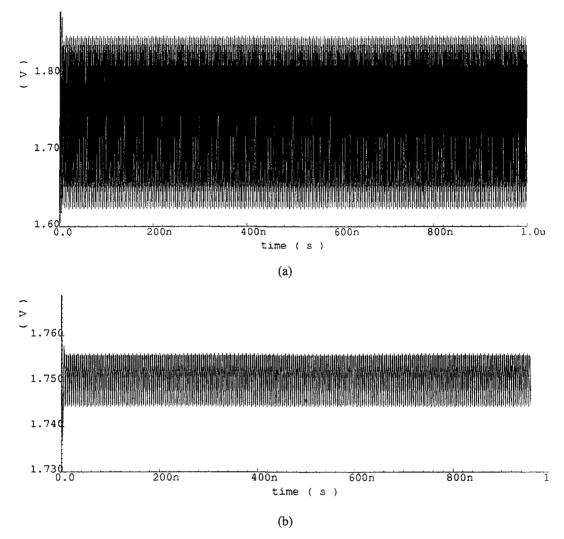

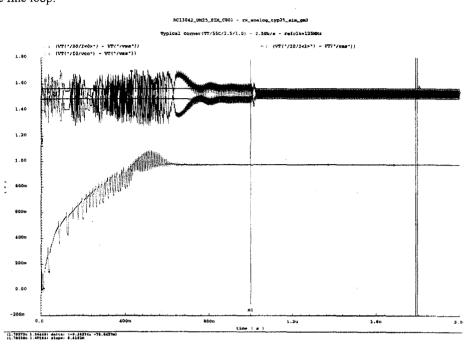

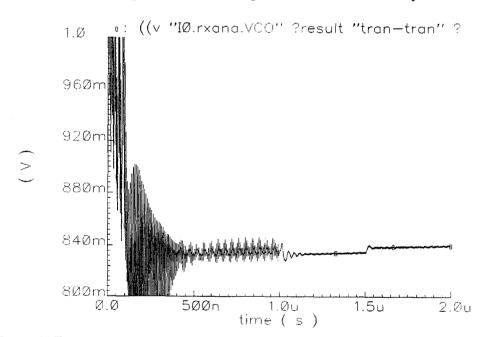

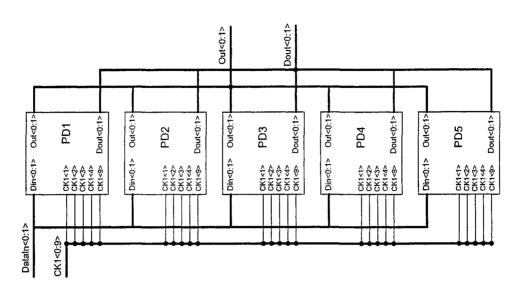

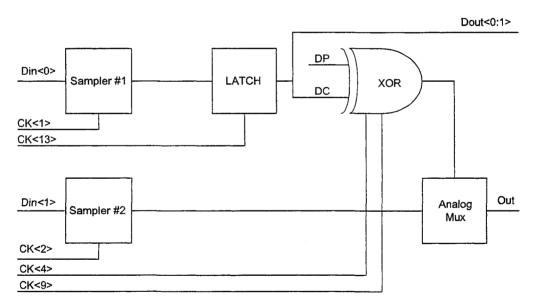

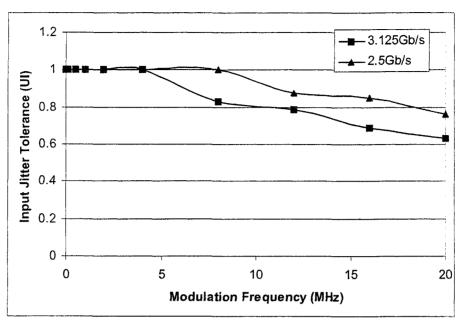

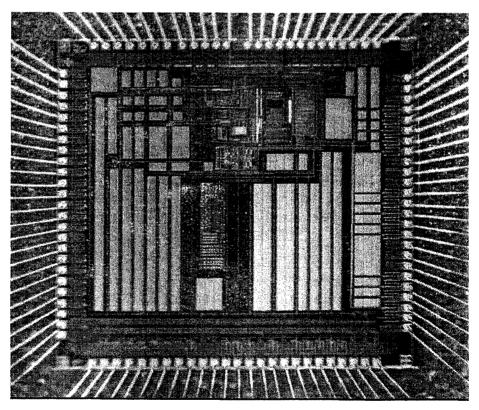

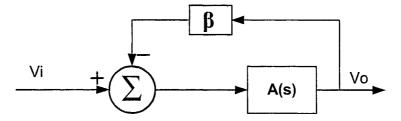

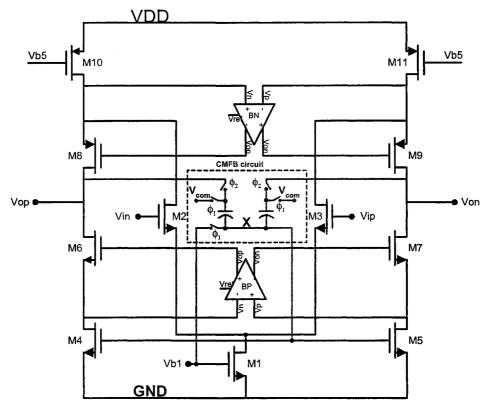

Figure 29 Operational amplifier circuit in tracking mode.